## Agence Nationale de la Sécurité des Systèmes d'Information

## Université GRENOBLE ALPES

Habilitation à diriger les recherches présentée par Guillaume Bouffard

Soutenue le 23 septembre 2025

Discipline Informatique et mathématiques appliquées

## Contributions à la sécurité des logiciels embarqués dans la chaîne de confiance

#### Composition du jury

Rapporteurs Jean-Max Dutertre Professeur, École des Mines de Saint-Étienne

Aurélien Francillon Professeur, EURECOM

Patrick Schaumont Full professor, Worcester Polytechnic Institute

Examinateurs Jessy Clédière Directeur de recherche, CEA Centre de Grenoble

Karine Heydemann Senior scientist, Thales CDI et chercheuse HDR associée au LIP6/Sorbonne Université

Marie-Laure Potet Professeure des Universités, Grenoble INP - Université Grenoble Alpes

Sébastien VARRETTE Responsable de laboratoire, Agence Nationale de la Sécurité des Systèmes d'Information

| Colophon                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mémoire de thèse intitulé « Contributions à la sécurité des logiciels embarqués dans la chaîne de confiance », écrit pa Guillaume Bouffard, achevé le 3 septembre 2025, composé au moyen du système de préparation de document ETEX e de la classe yathesis dédiée aux thèses préparées en France. |

|                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                    |

## Remerciements

Au milieu de l'hiver, j'apprenais enfin qu'il y avait en moi un été invincible.

Albert Camus. L'Été. 1954

On dit souvent que le plus important dans un voyage n'est pas la destination, mais le chemin parcouru. Ou, pour reprendre les mots d'Orelsan, « c'qui compte c'est pas l'arrivée, c'est la quête » 1.

Cette Habilitation à Diriger les Recherches (HDR) n'est pas seulement un point d'aboutissement. Elle est aussi la trace d'années de travail, de découvertes, d'essais et d'erreurs, mais surtout de rencontres. Sur cette route, il y a eu des guides bienveillants, des compagnons de route fidèles, des éclaireurs qui ont ouvert de nouvelles perspectives et des alliés qui ont tendu la main dans les moments d'incertitude. C'est à vous que je veux adresser ces lignes, pour vous dire que chacun de vos gestes, conseils, critiques ou encouragements a compté. Ce manuscrit porte vos empreintes autant que les miennes.

Je tiens à remercier les membres de mon jury pour avoir accepté de consacrer leur temps et leur expertise à l'évaluation de ce travail. Merci à Jean-Max Dutertre, Aurélien Francillon et Patrick Schaumont d'avoir accepté de rapporter cette HDR, ainsi qu'à Jessy Clédière, Karine Heydemann, Marie-Laure Potet et Sébastien Varrette d'avoir accepté d'en examiner le contenu et d'enrichir la réflexion par leurs retours. Je veux adresser à Karine et Marie-Laure une reconnaissance particulière : leur soutien et leurs encouragements, dans les moments décisifs, m'ont donné l'élan nécessaire pour mener ce travail jusqu'à son terme. Je tiens également à remercier Paolo Maistri pour son soutien à l'organisation de ma soutenance.

I would like to express my sincere gratitude to Patrick Schaumont for his time, insightful feedback, and valuable perspective on my HDR work. His expertise and thoughtful comments have greatly contributed to the quality and depth of this manuscript.

Dans cette quête, certaines rencontres changent définitivement la route. Pour moi, Jean-Louis Lanet en fait partie. C'est lui qui, alors que j'étais en master, m'a ouvert les portes de la recherche en sécurité informatique, me donnant l'envie d'explorer ce domaine encore inconnu. Il a ensuite accepté de diriger ma thèse de doctorat, m'accompagnant avec exigence, bienveillance et passion. Au fil des années, il est devenu bien plus qu'un directeur de thèse : un mentor et un ami, présent dans les moments décisifs comme dans les détours imprévus. Bien qu'il ait quitté depuis longtemps les routes académiques, son empreinte demeure dans chacune de mes étapes, comme ces balises que l'on croise au détour d'un chemin et qui rappellent la voie à suivre.

Mon arrivée, en 2014, à l'Agence Nationale de la Sécurité des Systèmes d'Information (ANSSI) a

<sup>1.</sup> ORELSAN, « La Quête », Civilisation, Warner Chappell Music France, nov. 2021.

iv Remerciements

marqué le début d'un nouveau chapitre dans cette quête. Dès mes premiers pas, j'ai eu la chance d'y trouver le soutien d'Eliane JAULMES, responsable du Laboratoire Sécurité des Composants (LSC), puis de Sébastien VARRETTE accompagné d'Alain Ozanne, son adjoint, en charge du Laboratoire Architectures Matérielles et Logicielles (LAM). Tous trois ont su tempérer parfois mes élans et m'ouvrir des chemins que je n'aurais pas explorés seul.

Je souhaite également remercier les différentes strates managériales de l'ANSSI : José Araujo, Eric Saliba, Aline Gouget, Renaud Labelle, Annaïg Andro et Vincent Strubel, dont les interrogations et les échanges, parfois en marge de mes travaux, m'aidant à affiner ma direction et à faire mûrir mes réflexions.

À l'ANSSI, j'ai eu la chance de croiser de nombreux compagnons de route qui, chacun à leur manière, ont guidé mes réflexions, éclairé mes doutes ou enrichi mes idées. Je souhaite remercier tout particulièrement les membres que j'ai croisés au LSC: Karim Khalfallah, Romain Poussier et Franck Rondepierre

En janvier 2023, ma quête m'a conduit jusqu'au LAM. Après un long chemin, j'y ai trouvé une oasis : un lieu où la bienveillance et la confiance de chacun ont offert l'espace et la sérénité nécessaires pour travailler à cette HDR. Je souhaite remercier chaleureusement Olivier Bal-Pétré, Luc Bonnafoux, Nicolas Bouchinet, François Jolivet, Gabriel Kerneis, Serge Lottiau, Arnauld Michelizza, Stéphane Neveu, Alain Ozanne, Philippe Trébuchet et Sébatien Varrette, dont le soutien, les échanges et les encouragements ont été comme une eau claire pour nourrir mes réflexions et faire mûrir mes idées.

Je tiens également à remercier l'ensemble de l'équipe du Centre de Certification National, et plus particulièrement Géraldine Avoué, Soline Renner et Jérôme Vidal, dont la disponibilité et la qualité des échanges ont été d'une aide précieuse sur mon chemin. Je n'oublie pas Valentin Houchouas, Louisa Кнаті, José Lopes Esteves, Alexandre Magloire, Hugo Mania, Ange Martinelli et Philippe Valembois, compagnons de route chers à mon cœur, dont l'amitié demeure solide malgré les trop rares moments partagés.

Je veux aussi remercier Coralie Снавот, Arnaud Minart et Anne Protas dont l'écoute et la disponibilité ont été des appuis précieux. Ils font partie de ces présences discrètes qui, par de simples gestes, rendent les journées plus légères et permettent au voyage de se poursuivre avec sérénité.

Je souhaite également remercier celles et ceux qui ont embarqué avec moi dans les travaux présentés dans cette HDR. Mes doctorants, qu'ils aient déjà atteint le port ou qu'ils soient encore en pleine traversée, ont été des équipiers précieux et sont devenus des amis. À ceux qui ont déjà mené leur navire à bon port, Amélie Marotta, Vincent Giraud et Thomas Trouchkine, je garde en mémoire nos traversées parfois agitées mais toujours porteuses de découvertes. À ceux qui voguent encore sur cette mer d'incertitudes et de promesses, Jonah Alle Monne et Gwenn Le Gonidec, je me réjouis des horizons que nous allons encore explorer ensemble.

Aucune expédition ne se mène seul, et si les doctorants sont les équipages en mer, les co-encadrants sont les capitaines restés à terre, veillant à ce que le cap soit maintenu et que chaque traversée se déroule au mieux. Les thèses que j'ai dirigées ou co-dirige encore doivent beaucoup à ces partenaires de route, dont l'engagement et la vigilance ont été déterminants à chaque étape. Je tiens à exprimer ma profonde gratitude à Jessy Clédière, Damien Couroussé, Rachid Dafali, Mathieu Jan, Maria Méndez Real, David Naccache, Jean-Christophe Prévotet et Olivier Sentieys. Leur expertise, leur disponibilité et leur implication constante sont des phares dans cette aventure scientifique, éclairant la voie et rendant chaque arrivée possible.

Et puis, il y a celles et ceux qui, dans les coulisses, ont apporté leur savoir-faire et leur énergie à certains travaux présentés dans cette HDR. Comme des artisans du navire qui, parfois le temps d'une escale, contribuent à renforcer la coque, ajuster les voiles ou affiner les instruments, ils ont laissé leur marque sur ce voyage scientifique. Je tiens à remercier chaleureusement Ever Atilano Rosales, Yanis Belkheyar, Angie-Sofia Bikou, Léo Gaspard, Louiza Malki et Guillaume P., pour leur travail, leur impli-

Remerciements

cation et leur enthousiasme.

Au détour d'un sentier de cette quête, certaines rencontres se sont révélées précieuses et durables. Ces compagnons de route, d'abord croisés dans le cadre d'une collaboration, sont devenus des amis avec qui j'ai partagé bien plus que des objectifs scientifiques. Je tiens à remercier Yoann Chergui, Laura Coman, David El Baze, Hélène Le Bouder, Julien Eynard, Patrick Haddad, Nicolas Hugget, Ambre looss, Ronan Lashermes, Boris Simunovic, Adrian Thillard Victor Lomné et Besma Zeddini pour les discussions passionnées, les instants complices et l'amitié qui perdure bien au-delà de nos projets communs.

Je n'oublie pas celles et ceux qui ont pris le temps de relire ce manuscrit pour l'améliorer et le rendre aussi clair et précis que possible. Leur regard attentif a permis de gommer bien des aspérités et de renforcer la cohérence de l'ensemble.

Enfin, je veux remercier mes amis Mohamed Amine Bouazzouni, Jean Dubreuil, Tom Khefif, Damien Marion et Tiana Razafindralambo, qui ont toujours cru en moi et m'ont rappelé, à chaque étape de ce voyage, que la confiance et l'amitié sont des forces aussi précieuses que le savoir.

Aucune quête ne se mène sans un port d'attache solide. Je souhaite remercier ma sœur Jennifer et son conjoint Cyril, pour leur présence et leur soutien discret mais constant. Je remercie également mes parents, qui m'ont donné le goût de la curiosité et la force d'aller au bout de mes projets. Et, plus que tout, je veux exprimer toute ma gratitude à Anne, ma merveilleuse femme, pour sa patience, son écoute et son indéfectible soutien dans les moments calmes comme dans les tempêtes. Sans vous, cette aventure n'aurait pas eu la même saveur.

Si cette HDR marque une étape, elle reste avant tout une invitation à poursuivre la quête, ensemble.

vi Remerciements

## **Acronyms**

A|B|C|D|E|F|G|I|J|L|M|O|P|R|S|T|V

## **ADAS** Advanced Driver Assistance Systems 60 APDU Application Protocol Data Unit 22-24 API Application Programming Interface 18, 19, 21, 24, 31, 109 ASIC Application-Specific Integrated Circuit 34, 38, 39, 58, 89 В BCV Byte Code Verifier 15-20, 52 $\mathbf{C}$ CAN Controller Area Network 61, 62 **CFI** Control Flow Integrity 32, 46, 49, 50 CFSSI Centre de Formation à la Sécurité des Systèmes d'Information 87, 88 CHERI Capability Hardware Enhanced RISC Instructions 32, 46, 49 **CoT** Chain of Trust 1, 3–7, 11, 22, 29, 43, 51–54, 56, 61–63, 88 **CPU** Central Processing Unit 2, 5–9, 12, 13, 26–36, 38, 40, 41, 44, 49, 51–59, 110 D **DRM** Digital Rights Management 3, 6, 9, 89 Ε EMFI Electromagnetic Fault Injection 38, 90 ENS Ecole Normale Supérieure 85, 86, 91, 93 FPGA Field-Programmable Gate Array 34, 38, 39, 89, 90, 93 $\mathbf{G}$ GPU Graphics Processing Unit 31, 32, 49

```

IoT Internet of Things 14

ISA Instruction Set Architecture 26, 33, 35–37, 39, 41, 53, 54

ITSEF Information Technology Security Evaluation Facility 1, 12–14, 23, 52, 86, 88

J

JCDK Java Card Development Kit 17-19

JCVM Java Card Virtual Machine 1, 7, 12, 14–21, 23–25, 52, 90, 109

JVM Java Virtual Machine 14, 16, 109

LAM Hardware and Software Architectures Lab 1, 51, 85, 92

LSC Hardware Security Lab 1, 51, 85, 93

Μ

MMU Memory Management Unit 32, 36, 44, 49, 50

MPU Memory Protection Unit 21

o

OS operating system i, 4, 12–15, 17, 19–21, 24, 25, 29–31, 37, 43–46, 48, 50, 55

OTP One-Time Password 2, 12

P

PAC Pointer Authentication Code 32, 46, 49, 50

PIM Platform Integrity Module 2, 3

PMU Power Management Unit 40, 41, 49, 53

R

R&D Research & Development 1

REE Rich Execution Environment 4–7, 9, 10, 29–32, 40, 41, 43–56, 59, 61–63, 88, 89

RoT Root of Trust 1–9, 11, 12, 22, 26, 28–30, 41, 43–45, 51, 52, 54, 56–59, 61–63, 88, 89

RTL Register Transfer Level 34, 38, 39, 58

S

SE Secure Element 2, 5, 7, 11–18, 20, 22–31, 40, 47, 51–53, 57–59, 61, 63, 88, 109

SGX Software Guard eXtensions 4

\textbf{SoC} \ \ \textbf{System-on-Chip} \ \ 2, \ 7, \ 9, \ 12, \ 29-33, \ 36, \ 40, \ 41, \ 49, \ 53, \ 56, \ 57, \ 59, \ 63, \ 90, \ 92

Т

TEE Trusted Execution Environment 4-9, 11, 28-32, 40, 41, 43-46, 48-56, 58, 59, 61-63, 88-91

TPM Trusted Platform Module 2, 3

VPU Video Processing Unit 31, 32, 49

```

## **Contents**

| R  | eme                                                                               | rciements                                                 | iii |  |  |

|----|-----------------------------------------------------------------------------------|-----------------------------------------------------------|-----|--|--|

| A  | cron                                                                              | yms                                                       | vii |  |  |

| C  | onte                                                                              | ents                                                      | i   |  |  |

| Li | List of Figures                                                                   |                                                           |     |  |  |

| 1  | Int                                                                               | roduction                                                 | 1   |  |  |

|    | 1.1                                                                               | Background                                                | 1   |  |  |

|    | 1.2                                                                               | Research Context                                          | 5   |  |  |

|    | 1.3                                                                               | Challenges                                                | 5   |  |  |

|    | 1.4                                                                               | My Contributions                                          | 6   |  |  |

|    | 1.5                                                                               | Organization of this Manuscript                           | 9   |  |  |

| 2  | Contributions to the Hardware Root of Trust Security                              |                                                           |     |  |  |

|    | 2.1                                                                               | Common Secure Element Architecture                        | 12  |  |  |

|    | 2.2                                                                               | Security of the On-Chip Operating System Layout           | 14  |  |  |

|    | 2.3                                                                               | Security Analysis of the Input/Output Interfaces          | 22  |  |  |

|    | 2.4                                                                               | Analysis of CPU Security Against Hardware Attacks         | 26  |  |  |

|    | 2.5                                                                               | Conclusion and Perspectives                               | 28  |  |  |

| 3  | Cor                                                                               | ntributions to the Trusted Execution Environment Security | 29  |  |  |

|    | 3.1                                                                               | Common Trusted Execution Environment Architecture         | 30  |  |  |

|    | 3.2                                                                               | Hardware Architecture of Application Processors           | 31  |  |  |

|    | 3.3                                                                               | Impact of Hardware Attacks on High-Perfomance Processors  | 33  |  |  |

|    | 3.4                                                                               | Impact of Environment on Application Processors Security  | 40  |  |  |

|    | 3.5                                                                               | Conclusion and Perspectives                               | 41  |  |  |

| 4  | Contributions to Execute Sensitive Applications in the Rich Execution Environment |                                                           |     |  |  |

|    | 4.1                                                                               | Common Rich Execution Environment Architecture            | 44  |  |  |

|    | 4.2                                                                               |                                                           | 45  |  |  |

|    | 4.3                                                                               | Rich Execution Environment Hardware Security Challenges   | 49  |  |  |

|    | 11                                                                                | Conclusion and Perspectives                               | 50  |  |  |

| ii | Contents |

|----|----------|

|    |          |

| 5  | Conclusion and Perspectives                             |  |

|----|---------------------------------------------------------|--|

|    | 5.1 Summary of Activities Introduced in this Manuscript |  |

|    | 5.2 Perspectives                                        |  |

|    | 5.3 Conclusion                                          |  |

| Bi | ibliography                                             |  |

| Α  | Curriculum vitæ                                         |  |

|    | A.1 Administrative Information                          |  |

|    | A.2 Professional Experience and Degrees                 |  |

|    | A.3 Teaching                                            |  |

|    | A.4 Research Activities at ANSSI                        |  |

|    | A.5 Scientific Responsibilities                         |  |

|    | A.6 Full List of My Publications                        |  |

|    | A.7 Ph.D. Thesis Reports and Defense Minutes            |  |

| G  | lossary                                                 |  |

## **List of Figures**

| 1.1        | Different use cases of hardware Root of Trust                                                                          | 3  |

|------------|------------------------------------------------------------------------------------------------------------------------|----|

| 1.2        | Classic Chain of Trust architecture based on hardware Root of Trust                                                    | 4  |

| 1.3        | Overview of my research activities                                                                                     | 7  |

| 2.1        | Overview of the Secure Element hardware and software architecture                                                      | 12 |

| 2.2        | Overview security model of the Java Card technology.                                                                   | 15 |

| 2.3        | Java Card method resolution process                                                                                    | 18 |

| 2.4        | Ambiguity in Method Resolution                                                                                         | 19 |

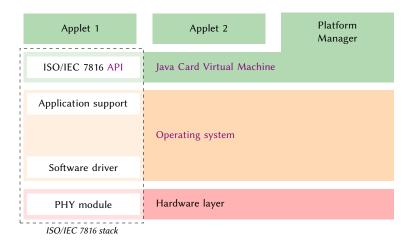

| 2.5        | ISO/IEC 7816 protocol layers                                                                                           | 23 |

| 2.6        | Overview of ISO/IEC 7816 stack architecture embedded in a Secure Element upon each software level                      | 24 |

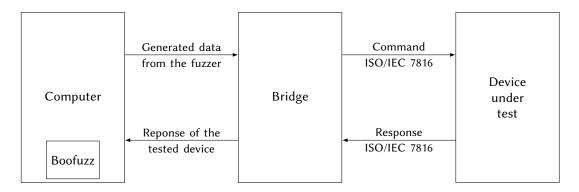

| 2.7        | Fuzzing architecture of ISO/IEC 7816 protocol.                                                                         | 25 |

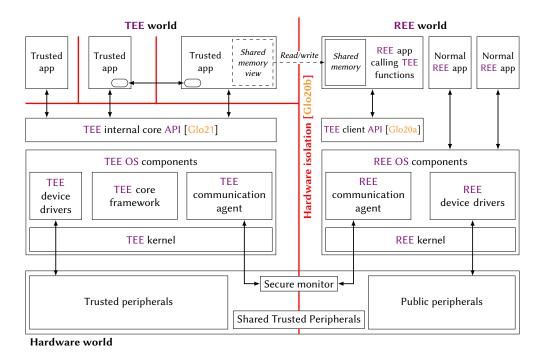

| 3.1        | Common Trusted Execution Environment software architecture                                                             | 31 |

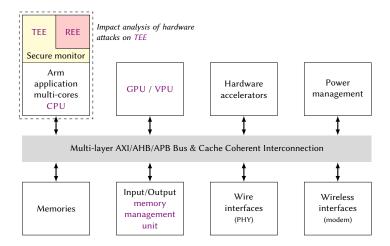

| 3.2        | Overview of application System-on-Chip hardware and software architecture                                              | 32 |

| 3.3        | Fault propagation through digital device abstraction layers with examples of fault effects and characterization levels | 34 |

| 3.4        | Top-down approach to characterize fault effects on in-order application processors                                     |    |

|            | micro-architecture blocks.                                                                                             | 35 |

| <b>4</b> 1 | A common Rich Execution Environment architecture                                                                       | 45 |

iv List of Figures

## **Chapter 1**

## Introduction

This habilitation to supervise research thesis provides an overview of my research activities at the National Cybersecurity Agency of France (ANSSI) Expertise department. After earning my Ph.D. in October 2014, which focused on analyzing the security of Java Card Virtual Machine (JCVM) implementations embedded in hardware Roots of Trust (RoTs) against both software and hardware attacks, I joined the ANSSI in November 2014. There, I became expert in the ANSSI Research & Development (R&D) labs, initially in the Hardware Security Lab (LSC) and later in the Hardware and Software Architectures Lab (LAM).

I have expanded my research to encompass the security of embedded software implementations deployed in each element of the Chain of Trust (CoT), addressing threats from both software and hardware attacks. While the litterature mainly focus on the security of cryptographic implementations, the security of embedded software has been less studied. My research aims to address this gap and to anticipate the risks targeting each element of a CoT. In particular, we have analyzed several implementations and discovered vulnerabilities in both their hardware [Tro+21] and software [DB21]. We also proposed several countermeasures to fix them. For example, in the field of hardware RoT, my contributions have significantly enhanced the robustness of security products [LB15]. This has encouraged developers to strengthen their solutions, Information Technology Security Evaluation Facilitys (ITSEFs) to broaden their criteria [DB21; Idr+17] and end-users to benefit from greater security.

## 1.1 Background

In our daily lives, we frequently perform sensitive operations, such as online banking, secure communication, or accessing private information. These activities require a secure host to protect sensitive data against unauthorized access or tampering. This host must provide a trusted environment, ensuring that information cannot be extracted and security functions remain uncompromised. To achieve this level of trust, such an element serves as a foundational component known as a RoT. A RoT acts as the cornerstone for building a secure environment where sensitive functions are executed.

One of the most familiar examples is the Secure Element (SE), commonly seen in smart cards used for payments or identity verification. Today, RoTs are prevalent, embedded in a wide range of devices such as computers, vehicles, TVs, video game consoles, and smartphones.

### 1.1.1 The Root of Trust

The RoT is defined by GlobalPlatform [Glo18b] as a combination of a computing engine, code, and potentially associated data co-located on the same platform, designed to provide foundational security services. These components are implicitly trusted as the base of a platform's security architecture, meaning their integrity and behavior cannot be verified by any preceding component.

For the purpose of this manuscript, I have intentionally defined the RoT as the minimal component that is accessible and suitable to meet the needs of ANSSI beneficiaries. This level of granularity ensures that the research presented here remains relevant and applicable. It is crucial that the elements studied are representative of components commonly available on the market.

Critical security functions in an information system are built upon the RoT. It serves as the foundation for establishing trust within the system, ensuring that security operations, such as authentication and integrity verification, are carried out reliably and securely. To guarantee this trust, the RoT must be inherently trustworthy, which is often verified through a high-level security evaluation performed by a third party. Such assessments, typically conducted under the Common Criteria security evaluation scheme [Eur14; Eur22], demonstrate the RoT's resilience against highly sophisticated attackers. Additionally, an attestation system [Adv23; Int21] is generally employed to assert the authenticity of the RoT and validate the platform version.

To ensure comprehensive security, a system must be secure from the hardware layer to the software layer. RoT is often implemented as a hardware secure module [Ram23]. This module can be a silicon-based hardware component embedded into a System-on-Chip (SoC) or a discrete component on the same motherboard as the system's main Central Processing Unit (CPU).

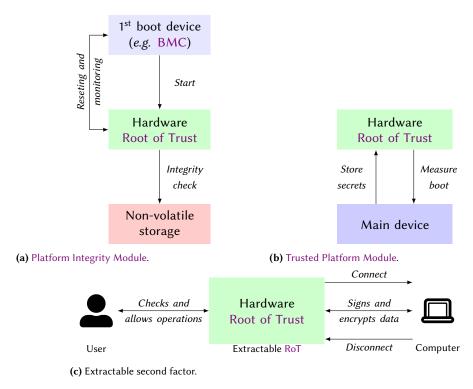

A hardware RoT supports key use cases [Ope23], such as verifying system integrity, performing a measured boot as part of a secure boot process, and serving as an extractable second factor for authentication, as introduced in Figure 1.1. Firstly, verifying system integrity means making sure that the system's hardware and software have not been tampered with, thus ensuring the trustworthiness of the computing environment. In this context, the RoT is known as Platform Integrity Module (PIM), as illustrated in Figure 1.1a. Secondly, performing a measured boot as part of a secure boot process entails measuring and recording the state of the system components during the boot sequence, which helps in detecting and preventing unauthorized modifications. For this use case, the hardware RoT is referred to as Trusted Platform Module (TPM), as introduced in Figure 1.1b. Lastly, serving as an extractable second factor for authentication provides an additional layer of security by requiring a physical token or device, in addition to a password to authenticate users, thereby enhancing protection against unauthorized access, as shown in Figure 1.1c. Such devices can also be used to securely store secrets like One-Time Passwords (OTPs), SSH or GPG keys, and even passwords, providing a secure enclave for sensitive data

1.1. Background 3

and further strengthening the overall security.

Figure 1.1: Different use cases of hardware RoT, inspired by [Ope23].

To minimize the attack surface, current implementations of hardware RoTs deliberately limit embedded features, often by restricting the device to execute only one application at a time to ensure secure operations. This approach significantly reduces performance and functionality. Such hardware RoTs alone are insufficient to meet the demands of modern applications, like streaming Digital Rights Management (DRM)-protected videos or encrypting data for cloud storage. To effectively balance high performance with robust security, it is essential to deploy a CoT that integrates multiple layers of RoTs, allowing for a more flexible and comprehensive security architecture.

#### 1.1.2 The Chain of Trust

A CoT [Glo19] is a sequence of trust relationships that originates from a RoT and extends through various levels of security elements within a performance-oriented system. Each element in the chain verifies the next component, insuring the integrity and trustworthiness of the entire system. This hierarchical approach allows for a scalable and secure architecture, where multiple layers of hardware and software security can be implemented, each offering different levels of assurance and protection. The CoT is crucial in complex systems where diverse security requirements must be addressed. Figure 1.2 provides an overview of a modern, high-performance runtime environment tailored for mainstream consumer applications, based on a multi-stage CoT.

**Figure 1.2:** Classic CoT architecture based on hardware RoT. This architecture is generally implemented as-is in smartphones, laptops and cloud servers.

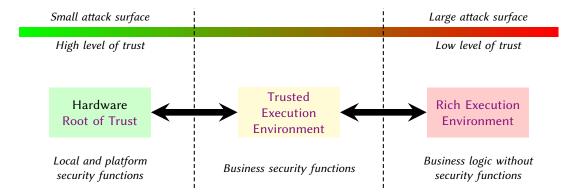

Each element that composes a CoT is designed to provide specific security features for the entire system, determined by the level of trust placed in the element and its security assurance level. A CoT can be divided into the following components:

**Hardware RoT** The hardware RoT, as introduced in Section 1.1.1, is the cornerstone of the security of the entire system. With a small attack surface and high security level, hardware RoTs provide *local and platform security functions*, such as secure boot [ANS23; App24] and platform key management [Int15].

Trusted Execution Environment (TEE) TEEs are initially designed to emulate the functionality of hardware RoTs, focusing on performance and resistance to tampering from software attacks [AF04]. Modern TEEs implementations such as AMD Security Processor [AMD23], Arm TrustZone [Arm17], and Intel Software Guard eXtensions (SGX) <sup>1</sup> [Int22a] claim to be resistant to software attacks. However, there are documented cases where vulnerabilities in these TEE implementations have been exploited through sophisticated software attacks [Cer+20; Sch+24]. Additionally, the TEE protection profile [Glo20b] has evolved to address resistance to some hardware attacks, recognizing the increasing sophistication of threat models [Jac+23; TSS17]. Despite these developments, no widely deployed TEE implementation have yet demonstrated resistance to a many of hardware attacks.

TEEs are primarily designed to run *business security functions* for applications running in the Rich Execution Environment (REE).

**Rich Execution Environment (REE)** The REE represents the final layer in the CoT, where high-performance applications operate. These applications are typically executed on modern operating systems (OSes) such as Linux or Windows for computers and servers, and Android or iOS for smartphones.

Modern OSes employ hardware-based security mechanisms, including memory protections and

<sup>1.</sup> Intel SGX has been deprecated on 11<sup>th</sup> and 12<sup>th</sup> generation Intel Core processors since 2021 [Tou22], although its development continues for Intel Xeon processors targeting cloud and enterprise applications [Rao22].

1.2. Research Context 5

control-flow integrity, provided by the system CPU, to safeguard running software. However, the complexity of the runtime environment often makes comprehensive security assurance challenging. Applications in the REE generally focus on *business logic without security functions*, with security responsibilities commonly offloaded to TEEs or hardware RoTs via the TEE. Nevertheless, when developers of high-performance applications lack access to TEE or hardware RoT, they are compelled to implement security mechanisms within the REE itself. This issue is further explored in Section 1.3.

## 1.2 Research Context

In late 2014, SEs, such as smart cards, were the most widely used security components for executing sensitive operations. These components serve as hardware RoTs, ensuring local and platform security functions.

However, towards the end of the 2010s, there was a significant shift in the landscape of secure computing. Sensitive operations increasingly started being executed outside of traditional SEs, within the main system's CPU, inside TEEs. This shift was driven by the growing complexity and performance demands of applications. As a result, there was a need to develop new architectures that extended trust beyond the boundaries of SEs, leading to the adoption of systems based on a CoT.

By the early 2020s, the nature of security threats had evolved. Initially, attacks that were traditionally targeted at SEs began to be adapted and applied to TEEs [Vas+20; YSW18]. TEEs, designed to provide a secure and high-performance area within the main processor for executing sensitive tasks, started to face sophisticated attacks [TSS17] as they became more widely used. As attackers continued to evolve their methods, these threats also began to target REEs [Bos+16], which are the standard operating environments where most applications run. The adaptation of these attacks highlighted the need for comprehensive security strategies that not only protect SEs and TEEs but also ensure the integrity and security of the entire CoT, including the REE.

Moreover, the general public increasingly relies on digital technologies for daily operations such as banking, shopping, and communication. This widespread adoption of digital services amplifies the importance of having a secure CoT. Ensuring that all components of the CoT are robust against security threats is crucial to protect users' sensitive data and maintain trust in digital systems.

## 1.3 Challenges

My research activity focuses on improving the security features introduced in Figure 1.2. These activities are divided into three main challenges.

Research question 1: How are *local and platform security functions*, provided by hardware RoT, developed and used to enhance security? During my Ph.D. thesis [Bou14], I focused on the security of embedded software implementations within SEs. Following this, my research expanded to

explore the broader use of hardware RoTs. This involved studying how hardware RoTs are integrated inside a CoT from both developer and user perspectives. My goal is to anticipate potential risks and understand the critical role hardware RoTs play in maintaining security, ensuring that they are effectively utilized to safeguard sensitive operations.

Research question 2: How can high security levels be achieved in TEE, which provide high-performance environments for *business security functions*? The advent of TEEs in application CPUs, such as Arm TrustZone [Arm17], has significantly enhanced security for sensitive applications requiring performance. In 2015, the ANSSI certified the TEE protection profile [Glo20b], establishing a framework for evaluating the hardware and software implementations of TEEs. This certification marked an important step forward, despite the framework not fully covering hardware attacks. Concurrently, hardware attacks emerged as a notable threat [MBB16; TM17; TSW16; Vas+20] against application CPUs. These attacks, adapted from those traditionally targeting hardware RoTs, exploit the broader attack surface of application CPUs, making their protection more challenging.

Research question 3: How can sensitive applications with security features run in the REE, an environment focused on business logic without specific security functions? Often, third-party developers lack access to TEEs or hardware RoTs due to the absence of agreements with platform designers. In the REE, malicious behaviors such as tampering with the environment or unauthorized access to process memory can occur, making these binaries vulnerable to attacks under a white-box security model [Cho+02]. Consequently, platform users who install applications from the REE app store or manually often encounter obfuscated binaries. Such obfuscated binaries are commonly protected by DRM-based mechanisms, deployed for instance for video games, which provide anti-piracy and anti-cheating protections [KAS20; Yah23], and for audio and video streaming applications [App16; Wid17]. It appears also that some payment applications, ideally secured by TEE or hardware RoT, are deployed in the REE due to contractual limitations, significantly elevating security risks, a concern acknowledged by the Payment Card Industry [Pay20]. The scientific community actively monitors these applications to detect vulnerabilities first [Bar+22; Heu24; PSF22]. According to Thomas [Tho22], the security race between updates and the exploitation of both known and unknown vulnerabilities is critical. Highlighting the significant risks of employing such environments for sensitive tasks underlines the significance of my prospective research to evaluate and mitigate these risks. This area is interesting for assessing the viability of using obfuscated binaries as a RoT in the REE.

## 1.4 My Contributions

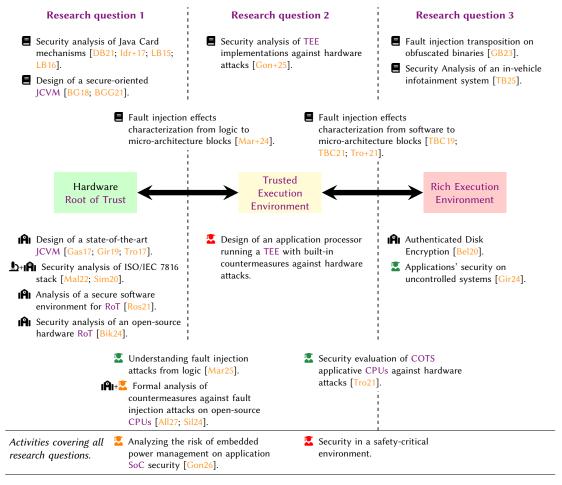

To provide a global overview of my research activities, Figure 1.3 displays my significant publications along with the supervisions (Ph.D. theses, apprenticeships, and internships) I have participated in.

1.4. My Contributions 7

Figure 1.3: Overview of my research activities, based on Figure 1.2. This figure shows my publications (indicated by the licon) at the top, categorized according to CoT elements, and various supervision activities at the bottom. Regarding supervisions, internships are represented by left, apprenticeships by left, and ongoing Ph.D. supervisions by the orange icon. Completed Ph.D. theses are marked by a green icon. Finally, the red icon represents Ph.D. projects that I plan to initiate as soon as possible.

During my research activities, I address simultaneously studies on each CoT element, engaging in applied research where I cover each challenge introduced in Section 1.3.

## 1.4.1 Contributions to Hardware Root of Trust Security

My research was initially focused on the security of software layouts embedded in hardware RoT, specifically on SE RoT implementations. Building upon the SE foundations laid during my Ph.D. thesis [Bou14; Idr+17], I examined the security of Java Card platform implementations, which are extensively embedded in SE. I pushed further these studies to scrutinize the security of each mechanism interacting with the Java Card platform, as outlined in the Java Card protection profile [Ora21c]. Particularly, I investigated the security of the compilation process [DB21] and the application verification process [LB15;

8 CHAPTER 1. Introduction

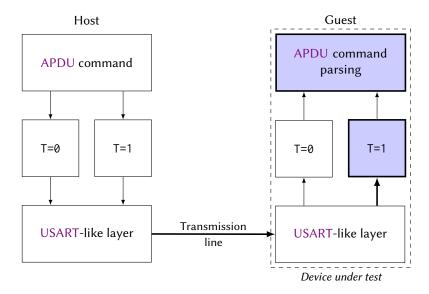

LB16] employed prior to loading applications. These studies uncovered vulnerabilities and eventually raised the Java Card platform security. Additionally, I studied the security of the communication protocol implementation, specifically the ISO-7816 stack, during the work with Simunovic's apprentice-ship [Sim20] and Malki's internship [Mal22]. I also investigated the security of CPU implementations against fault injection attacks with the supervision of Silva Araújo's internship [Sil24].

During security evaluations, I observed a trend among developers to favor organizational processes over technical solutions to mitigate security risks. Advocating for integrating protections directly into the execution environment, I aimed to achieve security that is less dependent on human factors. In the absence of an open reference implementation of the Java Card specification, I initiated the development of a state-of-the-art and modular Java Card platform version. This project was carried out during the internships of Gaspard [Gas17] and Giraud [Gir19]. Due to licensing constraints the source code is not public. This implementation includes innovations in security [BG18], memory management, and the compilation process [BGG21]. During Trouchkine's internship [Tro17], we implemented a dedicated hardware execution environment to assess the potential performance and security benefits of running Java Card applications natively. This involved developing a processor capable of directly executing Java Card bytecode as assembly, thereby opening new avenues to optimize both the execution efficiency and security of the Java Card platform.

## 1.4.2 Contributions to Trusted Execution Environment Security

Next, my research expanded to studying the security of TEE implementations embedded in application CPUs, a subject initiated during Trouchkine's Ph.D. thesis [Tro21]. This work aims to understand how hardware attacks can extract secrets from the TEE. While the TEE protection profile [Glo20b] acknowledges the need to address hardware attacks, no commercially deployed TEE implementation currently integrates countermeasures against them.

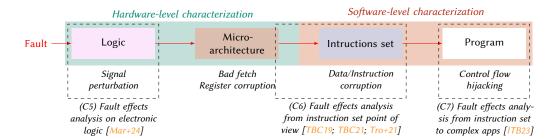

In Trouchkine's Ph.D. thesis [Tro21], we focused on assessing the potential and effects of fault injection attacks on application CPUs [TBC21; Tro+21]. Since we analyzed fault effects on COTS components without access to their internal implementations, we characterized these effects from the CPU's instruction set down to its micro-architecture blocks [TBC19]. During Marotta's Ph.D. thesis [Mar25], we further explored the impact of faults from a hardware logic perspective [Mar+24].

To advance this research, I aim to bridge the gap between the work initiated with Trouchkine and that conducted Marotta to achieve a comprehensive understanding of fault effects on application CPUs. This knowledge will be instrumental in developing efficient countermeasures spanning both software and hardware layers.

In parallel, Alle Monne's Ph.D. thesis [All27] focuses on evaluating the effectiveness of embedded countermeasures in hardware RoTs. His work represents a key step in assessing the security of application processors running a TEE and their resilience to fault injection attacks. In this study, we analyze the resistance of these implementations directly from their hardware source code, allowing for a deeper assessment of their robustness and potential vulnerabilities.

Additionally, in Gonidec's Ph.D. thesis [Gon26], we examine the implications of integrated power management modules on the security of TEEs [Gon+25]. By investigating how these modules can be manipulated to induce faults or leak sensitive information, we aim to identify vulnerabilities and propose mitigation strategies. The findings from this research could be extended to all hardware blocks embedded in application SoCs, including hardware RoTs and REEs, broadening its impact beyond power management security.

## 1.4.3 Contributions to Rich Execution Environment Security

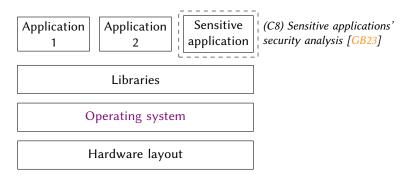

Finally, my research has broaden to analyzing sensitive applications running in the REE. These applications often lack access to hardware RoT or TEE, making them susceptible to white-box attack models [Cho+02]. In this context, during Giraud's Ph.D. thesis [Gir24], we explored the security of software in these environments. Our studies primarily focused on obfuscated applications, investigating them under the scope of reverse engineering tools where anti-reverse and anti-debug protections are implemented. Together with Giraud, we analyzed the feasibility and implications of transposing hardware attacks, mostly studied against hardware RoT, onto an obfuscated binary [GB23].

## 1.5 Organization of this Manuscript

This manuscript addresses the three challenges introduced in Section 1.3 through the following research questions. It is organized as follows:

- Chapter 2 describes my research activities related to the software layout embedded in hardware RoT. Extending the work begun during my Ph.D. thesis [Bou14], this chapter analyzes each component interacting with the RoT runtime environment, from the compilation process to the application and external communications of the RoT. It addresses the first research topic: How are local and platform security functions developed and used to enhance security?

- Chapter 3 discusses my activities about the TEE environment, particularly focusing on application CPU defenses against hardware attacks. Despite the current TEEs not being designed to be resistant against such attacks, the TEE protection profile [Glo20b] suggests they should be. Consequently, this chapter evaluates threats and designs efficient countermeasures that balance performance and security. It goes deeper into TEE security against advanced attackers as outlined by the TEE protection profile, aiming to answer the second challenge: How can high security levels be achieved in high-performance environments for business security functions?

- Chapter 4 examines the challenges of executing sensitive applications within the REE, an environment primarily designed for business logic without specific security functions. Due to the lack of access to TEEs or hardware RoTs, third-party developers must rely on alternative protection mechanisms, such as software obfuscation, DRM-based solutions, or hardware units provided by the application CPU. In this chapter, we analyze how sensitive applications can operate securely within an untrusted execution environment, evaluating the feasibility and effectiveness of various

10 CHAPTER 1. Introduction

protection techniques against potential threats. It addresses the third research topic: *How can sensitive applications with security features run in the REE, an environment focused on business logic without specific security functions?*

— Chapter 5 concludes this manuscript by outlining my future research perspectives.

## **Chapter 2**

# Contributions to the Hardware Root of Trust Security

In Chapter 1, we explored the essential role of hardware RoTs as the foundational element in establishing a CoT, crucial for securing computing environments against diverse threats. We now introduce how hardware RoTs ensure secure operations and protect sensitive data integrity and confidentiality within various systems, thereby enhancing trust in digital platforms.

Building upon these principles, this chapter describes my specific contributions towards advancing the security of embedded software in hardware RoTs. Given their critical function in initiating and maintaining a TEE, it is crucial to ensure the security of hardware RoTs and to forsee new attack vectors.

In the field of security technology, SEs are recognized as fulfilling all the requirements of a hardware RoT. These elements inherently provide a tamper-resistant environment, crucial for secure data storage and cryptographic operations, thereby establishing their keystone in hardware RoT implementations. As of 2018, GlobalPlatform estimated the deployment of approximately 55 billion SEs worldwide [Glo18a]. Moreover, both the hardware and software components of SEs undergo rigorous security evaluations under the Common Criteria scheme [Int22b]; each evaluation taking at least six months to one year with several experts involved. By 2023, about 200 products had been evaluated under this scheme within the European Union [Com24]. Given the vast number of deployed units and the stringent security requirements they satisfy, SEs is an optimal choice for my research, providing a solid foundation for the widespread application and validation of security principles.

This chapter outlines my contributions to enhancing the *security of software embedded in hardware RoT* with a main focus on SE implementations, beginning with an introduction to the hardware and software architectures of SEs in Section 2.1. This section highlights my advancements in SE security. The chapter is divided into three main sections: Section 2.2 introduces my contributions to the software layout, specifically focusing on Java Card technology; extensively deployed in SEs. Following that,

Section 2.3 investigates the security of input/output interfaces, analyzing potential vulnerabilities that could be exploited to extract information from SEs. Finally, Section 2.5 concludes this chapter by summarizing the findings and presenting my future directions in the security of hardware RoT.

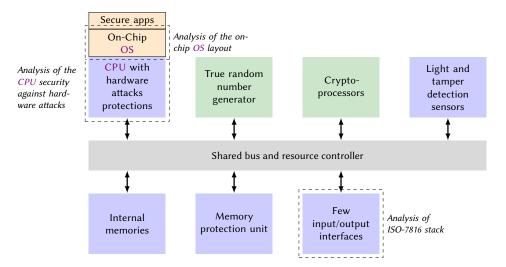

## 2.1 Common Secure Element Architecture

A SE is designed to resist to both hardware and software attacks, as outlined in its dedicated protection profile [Eur14]. In the event of an attack, it can erase non-volatile memory and enter a permanently disabled state to prevent further access. To achieve this, the SE integrates dedicated security hardware, including a cryptographic coprocessor, a true random number generator, tamper detection sensors, and typically a CPU with built-in protections against hardware attacks [Ars+20; CCH23; Wer+19]. These components are embedded in a low-performance SoC, named a microcontroller, as illustrated in Figure 2.1, and complemented by a hardened software stack. Most SEs also include a JCVM, ensuring a secure runtime environment [ZDS23]. The entire hardware and software stack undergoes rigorous security evaluations to comply with the requirements defined in the SE protection profile [Eur14].

**Figure 2.1:** Overview of the SE hardware and software architecture, adapted from the SE protection profile [Eur14]. Yellow boxes highlight the software layout, blue boxes represent general-purpose hardware, and green boxes indicate cryptographic hardware blocks, which are mainly focus of hardware attack literature [BB23; CX23; Pic+23]. The *Internal Memories* block, shown as a meta-block, may include SRAM, Flash, and OTP memory. Dashed boxes and italicized labels highlight my contributions to SE security.

During a security evaluation, an ITSEF conducts assessments under the supervision of a certification body and according to a public certification scheme, such as Common Criteria, or a private one, like EMVCo. The certification process evaluates the resilience of security functions deployed to protect sensitive assets against a defined level of attacker [Eur14; Eur22]. The target of evaluation and the attacker level are determined by the customer for whom the product under evaluation is developed. In

cases where several developers are involved in the design of a SE, the security evaluation can be carried out through composition. This approach involves analyzing one part of the target through an initial evaluation, while other parts undergo subsequent evaluations conducted by one or more ITSEFs. The use of composition not only eases a modular approach to security assessments but also permits for the specialization of security evaluations across different system components such as hardware, OSes, and applications. This modular method helps breaking down the security problem into small parts, making it manageable and focused on specific functions or layers within the system.

SEs which successfully pass security evaluations under the Common Criteria scheme, supervised by a national certification body, can achieve certifications up to the "Formally Verified Design and Tested" level [Car07]. In France, the national certification body is ANSSI.

Cryptography forms the cornerstone of security within SE, playing a critical role in ensuring the integrity, confidentiality, and authenticity of sensitive data. Security evaluations of SEs are conducted with respect to the current state of knowledge, which includes both publicly available scientific publications and restricted information. In the security analysis of SEs, robustness is primarily assessed in terms of cryptographic security against flawed practices [Nem+17] and hardware attacks [BB23; CX23; Pic+23].

However, the security of the software that utilizes these cryptographic implementations has received comparatively less attention to protect them against hardware attacks. This results in a more limited state of knowledge in this domain compared to the well-studied field of cryptographic implementations. This gap is significant, as these software components are responsible for initializing and managing cryptographic operations. In my research, I have aimed to address this gap by analyzing, understanding, and improving the software embedded in the SE.

My research on SE security is divided into three main areas: the *security of the on-chip OS*, as introduced in Section 2.2, the *security of input/output interfaces*, described in Section 2.3, and the *analysis of CPU security against hardware attacks*, presented in Section 2.4. In each section, I present my contributions along with associated perspectives.

## 2.2 Security of the On-Chip Operating System Layout

#### Associated contextual elements of this research field

Collaborations: Jean Dubreuil (SERMA, Pessac, France), Arnaud De Grandmaison (Arm, Paris, France),

Said El Hajji (LabMIA, Faculté des Sciences, Rabat, Morocco), Karine Heydemann (LIP6, Sorbonne University, Paris, France), Noreddine El Janati (LabMIA, Faculté des Sciences, Rabat, Morocco), Julien Lancia (Thales ITSEF, Toulouse, France), and

Jean-Louis Lanet (INRIA-LHS, Rennes, France).

**Publications:** [AG21; BG18; BGG21; DB21; Idr+17; LB15; LB16]

Supervisions: Internships of Léo Gaspard [Gas17], Thomas Trouchkine [Tro17], Vincent Gi-

raud [Gir19], and Ever Atilano Rosales [Ros21].

In SE security, having a comprehensive view of hardware and software security threats for complex applications is a challenging task. For example, most SEs embedded in smartcards have an EMVCo-compliant [EMV07; EMV08; EMV11a; EMV11b; EMV11c; EMV11d] application. Designing and securing state-of-the-art EMVCo-compliant applications for SE requires considering both hardware and software attacks. Developers of such applications must have multidisciplinary skills and expertise in both hardware and software security. Such a profile is extremely rare and software developers often lack the expertise to design complex applications.

The Java Card technology addresses this need by offering a standardized and secure on-chip OS that abstracts hardware security complexities, thereby enabling developers to focus on their application's features and to define protection requirements more clearly.

Java Card supports the development of secure applications regardless of specific hardware or OS models, enabling application developers to work without knowledge of the underlying platform specifics. This abstraction means that developers can focus solely on functionality and security without adapting to each target's characteristics. As a memory-safe language, Java Virtual Machine (JVM) also provides protections against common memory-related vulnerabilities, such as buffer overflows and invalid memory access, which enhances application security. For its time, Java Card brought the advantages of the Java language (security, portability, and simplified development) into a resource-constrained environment. This approach simplifies the development process, ensures uniform deployment across various devices, and effectively mitigates security risks associated with diverse hardware environments.

The Java Card technology is employed in the vast majority of evaluated SEs, with nearly 100 Java Card products evaluated annually under the French Common Criteria scheme. Since 2015, the Java Card technology has increasingly been targeted towards the automotive and Internet of Things (IoT) security sectors [Pas22]. According to [Pas22], 6 billion devices equipped with a JCVM are deployed annually. Java Card specifications, released and licensed by Oracle, have evolved to the current version 3.2. Throughout my research, I have studied Java Card versions from 2.2.2 to 3.0.5.

## 2.2.1 Overview of the Java Card Technology

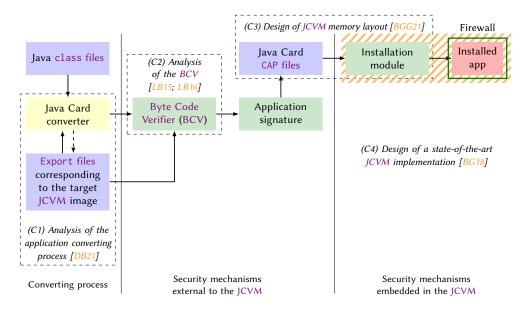

For software developers, Java Card follows the same development and compilation process as Java Standard Edition. Developers write applications in Java and compile them into class files using the javac compiler. As Java class files are not suitable for resource-constrained devices like SE, they must be converted into smaller CAP files using a Java Card converter. This process is shown on the left side of Figure 2.2.

**Figure 2.2:** This figure describes the Java Card architecture, divided into three sections: the conversion of Java class files for resource-constrained devices like SE, external and embedded security mechanisms within the JCVM. The color-coded blocks signify: blue for files involved in the compilation process to load applications into the JCVM, yellow for elements without security features, green for elements with security features, and red for the installed application in a JCVM. Since this application must access only authorized resources [Ora21c], the JCVM *Firewall*, shown as a green rectangle, enforces application segregation within a specific security context.

The security mechanisms are implemented both externally and internally to the JCVM. Externally, the BCV ensures that the structure and semantics of the Java Card CAP files comply with Java security rules, such as prohibiting pointer arithmetic. Internally, an installation module loads the Java Card CAP file into non-volatile memory, performing few checks close to those conducted externally, along with possibly additional verifications. Once these checks are complete, the installation module converts the CAP file into undocumented internal structures used by the JCVM implementation. Additionally, at runtime, the *Firewall* dynamically verifies access to resources, ensuring application isolation and adherence to security policies [Ora21b].

The common security evaluation target [Ora21c] for JCVM implementations is marked in an orange hashed rectangle (%). This part was studied during my Ph.D. thesis [Bou14].

Contributions from my post-Ph.D. work are highlighted in italic, with studied JCVM blocks shown in dashed boxes and started with the label (C1), (C2), (C3), and (C4).

The embedded JCVM implementation security relies on the a specific software validation done by the Byte Code Verifier (BCV) which checks for type correctness and memory access properties. Few checks occur at load time before CAP files are installed on the device. Most Java Card platforms do not include a BCV due to its high memory consumption, so verification is performed outside the device by the issuer or a trusted third party, as noted in the middle of Figure 2.2.

In addition to static verification, the Java Card Firewall ensures application isolation at runtime. It creates separate security contexts for each package, preventing unauthorized access between packages. This is depicted on the right side of Figure 2.2.

The Java Card architecture, along with the contributions I made after my Ph.D. thesis, are illustrated in Figure 2.2. During my doctoral research, we analyzed embedded implementations [Bou14; Idr+17]. Subsequently, I extended this work to focus on external security mechanisms for JCVM, as detailed in Section 2.2.2.

## 2.2.2 Analysis of the Java Card External Mechanisms

This section explores external mechanisms that protect JCVM implementations from software attacks and analyzes critical elements of Java Card security, which are often assumed to be trustworthy.

During my Ph.D. thesis [Bou14], we highlighted the BCV as a critical element of JCVM security. The BCV performs crucial security checks to ensure each embedded application complies with Java security rules. It targets the CAP file with two main checks: *type correctness*, which prevents prohibited type conversions through abstract interpretation, and *structure verification*, ensuring compliance with Java Card specifications [Ora21b]. Even a minor unchecked element in the CAP file can introduce significant security vulnerabilities into SE, as demonstrated in [FV10].

#### 2.2.2.1 Security Analysis of the Byte Code Verifier

### **Related publications**

- Julien Lancia and Guillaume Bouffard. "Java Card Virtual Machine Compromising from a Bytecode Verified Applet", In: CARDIS 2015 Article in PDF [LB15]

- Julien Lancia and Guillaume Bouffard. "Fuzzing and Overflows in Java Card Smart Cards", In: SSTIC 2016

Article in PDF [LB16]

Testing software thoroughly is complex, as it requires ensuring both test coverage and compliance of the code with the implemented specification. Efforts have been made to characterize the BCV of Java Standard Edition from both functional and security perspectives. The JVM dynamically calls the Java BCV during the loading of class files, verifying compliance and ensuring security before execution. For example, Sirer [Sir99] used code mutation and a reference JVM with BCV as an oracle for automatic test case generation. Similarly, Calvagna and Tramontana [CT13] developed a formal JVM model that includes BCV and used model-based testing to evaluate compliance.

The Java BCV and the Java Card BCV serve different purposes due to the distinct file formats and security constraints of Java Card compared to Java. Java Card supports a simplified subset of Java, but the Java Card BCV statically verifies that the application complies with security rules and adapts to the

targeted JCVM implementation security constraints. In contrast, the Java BCV is more generic, as it dynamically verifies each loaded class file, it can rely on the execution context to ensure compliance with security rules.

In the Java Card technology, implementations of both external [Ler02] and embedded [Ber+14; Cas02] Java Card BCV have been developed from formal specifications. These models are also used to test some part of the Oracle's closed-source Java Card BCV [CFT14; SFL13] implementation provides within the Java Card development kit; however, no comprehensive work has fully targeted the Java Card BCV.

Faugeron and Valette [FV10] analyzed Oracle's Java Card BCV version 2.2.2 using non-formal methods. Their work revealed a flaw in the interpretation of branch instructions, leading to undetected type confusion. This issue was subsequently patched in version 3.0.3. Their findings raised questions about the potential existence of other incorrect verifications not detected by the formal models used in the analysis, highlighting the need for further investigation into such vulnerabilities.

A Missing Check in the Byte Code Verifier To assess the application verification process by the BCV, we developed a fuzzing approach based on genetic mutation. Starting with a simple, legitimate application, we introduced mutations by randomly altering a byte in the application's CAP file for each test iteration. The BCV then evaluates whether the mutated CAP file remains valid. If it passes, the cref <sup>1</sup> attempts to execute the application associated to the mutated CAP file. Errors thrown by cref alert on the presence of a malformed application, which may expose security vulnerabilities. These CAP files undergo further detailed analysis. Employing this method, we uncovered a significant vulnerability across versions 2.2.2 to 3.0.5 of the BCV [LB15]. This contribution is labeled by (C2) in Figure 2.2.

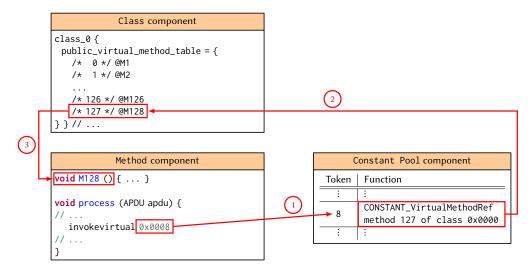

During the method resolution process, the runtime environment translates a token into an address, as detailed in Figure 2.3. Our testing approach revealed a critical missing check in the BCV: if an entry in the public virtual method table is missing, the BCV fails to raise an error. Some JCVM implementations may attempt to resolve this missing address by overflowing the public virtual method table, using the subsequent two bytes for address resolution. As demonstrated in [LB15], an attacker can exploit this behavior to redirect application control flow to a malicious payload.

This work was extended in [LB16], where techniques for executing polymorphic code were developed to conceal a payload within an application. This strategy becomes essential for an attacker when a third party performs comprehensive verifications on the application beyond the standard BCV checks, including specific requirements dictated by the target platform's security guidelines. Such an attack underlines the importance for third parties to conduct expensive verifications before loading applications onto a Java Card-based SE.

**Security Impact of a Missing Check in the Byte Code Verifier** The identified vulnerability involved a missing field check in the CAP file by the BCV, potentially exploitable on various JCVM implementations. We provide an attack path on a deployed JCVM implementation [LB15]. Due to many SE devices does

<sup>1.</sup> The cref is a reference Java Card simulator provided in the Java Card Development Kit (JCDK) and serves, in this work, as our fuzzing oracle.

**Figure 2.3:** This figure illustrates the Java Card method resolution process within a CAP file that encompasses Class, Method, and Constant Pool components, each essential to the operation. The Method component lists bytecode tokens; the Constant Pool provides linkage details for each token, specifying package, class, and method information. Resolution occurs when the JCVM retrieves the Constant Pool entry for a token, such as 0x0008, directing to the appropriate method in the public virtual method table field of the Class component. Red arrows marked as ①, ②, and ③ indicate the order of resolution.

not embedding a comprehensive and evaluated BCV, the embedded JCVM relies on external tools to ensure that applications meet Java Card specifications without doing on itself these checks. Oracle's BCV, adhering closely to Java Card standards, is widely used for this purpose.

We initiated a responsible disclosure with Oracle in early 2015. Oracle responded by releasing JCDK version 3.0.5u1 on August 19, 2015, and informed their customers. Conforming to the Java Card protection profile [Ora21c], all SE must use the latest BCV version. In compliance with Common Criteria procedures, certification bodies conducted pre-disclosure verifications on evaluated platforms. After confirming the mitigation of the vulnerability, we publicly disclosed the details.

#### 2.2.2.2 Security Analysis of the Class to CAP file Converting Process

## Related publication | Jean Dubreuil and Guillaume Bouffard. "PhiAttack - Rewriting the Java Card Class Hierarchy", In: CARDIS 2021 Article in PDF [DB21]

To perform the analysis of a CAP file, the BCV requires all export files from the target JCVM that will be imported by the application under review. However, export files lack integrity and authenticity assessment, posing security risks when validating potentially corrupted information. We highlighted these risks in [Bou+13a], noting consequences to counterfeit export files. We subsequently demonstrated a Man-in-the-Middle attack that exploits malicious export files to extract cryptographic keys. This involved installing a backdoored Application Programming Interface (API) on a JCVM, enabling it

to intercept and record keys generated by legitimate cryptographic APIs. However, this attack is easily detectable and thus not considered realistic.

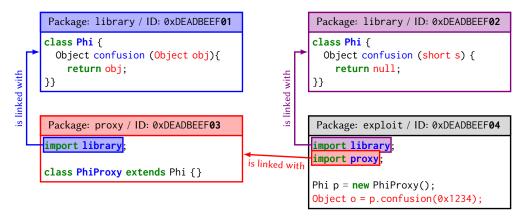

Ambiguity in Method Resolution Process In [DB21], we expanded our analysis to explore how the Java Card converter translates symbols from class files to CAP file. Symbols in class file are encoded as Unicode strings, while in CAP file, they are represented by 1- or 2-byte token values. We identified an ambiguity in the method resolution process that can be exploited in several JCVM implementations. This vulnerability, undetectable by the Java Card BCV, can be leveraged within legitimate uses of the JCDK. Refer to Figure 2.4. This contribution is named (C1) in Figure 2.2.

**Figure 2.4:** This figure illustrates a potential ambiguity in method resolution within Java Card platforms. The exploit package imports both the library package (purple, top right) and the proxy package (red, bottom left). The proxy package, in turn, is linked with a different library package (blue, top left), highlighting possible confusion during linking. At runtime, due to an implicit cast from the PhiProxy class to the Phi class, it becomes unclear whether a confusion method call in the exploit package is intended for the purple library or the blue library. This illustrates a security challenge in ensuring the correct method linkage.

In Java Card platforms, every package is identified by a unique identifier. Currently, there are no measures in place to prevent a developer from creating a package that shares a name with an existing one, as long as the new package's identifier is not already in use. Both during compilation and at runtime, this situation is manageable: the BCV can identify and differentiate between the two packages to ensure their correct usage. The JCVM interprets bytecode based on the content of CAP files, which import packages using their identifiers.

The code architecture shown in Figure 2.4 is accepted by the BCV. Both the blue and purple library packages include a confusion method with different signatures; one accepts an Object as parameter, the other a short. The BCV associates the confusion method in the exploit package with the purple library based on its export files, unaware that the proxy package links to a different library version. This misassociation causes the BCV to verify the method's signature incorrectly. When the confusion method is invoked, the JCVM dynamically resolves the call to the blue library via the class reference in the proxy package, leading to an erroneous execution of the blue library's method. As detailed in

Figure 2.4, this flaw enable us to craft a pointer from address 0x1234, exploiting the vulnerability.

**Security Impact of Ambiguity in Method Resolution Process** This section explains how the missing informations in both CAP files and export files can be exploited to circumvent BCV checks during method resolution. From the perspective of the Java Card converter, export files lack sufficient information to explicitly specify which packages are imported in CAP files, preventing the BCV from verifying correct method usage according to their signatures. The BCV delegates this verification to JCVM implementations, which in turn assumes that the BCV has already performed these checks.

Such vulnerabilities could allow an attacker to execute malicious code inside a verified application, undermining the Java Card security model. However, exploiting this vulnerability requires additional conditions, such as executing specific malicious payloads on targeted devices, as the only presence of overflow or underflow does not automatically imply the existance of an exploitable attack vector

One way to mitigate this issue is to restrict the use of export file format version 2.3, introduced in Java Card 3.1 revision, released a few months before our publication [DB21]. This updated export file format includes additional information about, for each class, the imported packages and version, addressing the issue identified. However, the latest versions of the BCV still accept export files from version 2.2. Enforcing the BCV to only accept export files from version 2.3 is not currently feasible. Notably, sensitive export files, such as those from GlobalPlatform [Glo12], are only available in version 2.2, posing a significant challenge for compliance and security.

The discovery of this vulnerability in export files undermines Java Card security and opens up new research directions for identify other potentially missing or incomplete checks. In line with our responsible disclosure policy, all Java Card platform developers potentially impacted by this vulnerability were informed through the Common Criteria scheme prior to public disclosure.

#### 2.2.3 Synthesis and Perspectives

This section has presented my contributions to the security of on-chip OS embedded in SE, with a primary focus on the Java Card platform's security. During security evaluations, a common trend I observed was the preference for organizational processes over technical solutions to mitigate security risks. To counter this, I advocate for integrating security measures directly into the execution environment to reduce dependency on human factors.

## 2.2.3.1 Perspectives in Java Card Platform Security

#### Related publications

- Guillaume Bouffard and Léo Gaspard. "Hardening a Java Card Virtual Machine Implementation with the MPU", In: SSTIC 2018 Article in PDF [BG18]

- Guillaume Bouffard, Vincent Giraud, and Léo Gaspard. "Java Card Virtual Machine Memory Organization: a Design Proposal", In: *arXiv* 2021 Article in PDF [BGG21]

Given the absence of an open reference implementation for the Java Card specification, I started the development of a state-of-the-art and modular JCVM. This project began during the internships of Gaspard [Gas17] and Giraud [Gir19]. Two significant results have been achieved.

First, advancements in the security of OS running the JCVM are presented in [BG18], highlighted as (C4) in Figure 2.2. This work explores how a Memory Protection Unit (MPU) can improve the Java Card Firewall to ensure applet segregation. We leveraged the MPU to segregate each applet within its own security context, preventing unauthorized access between applets. Most existing Java Card Firewall implementations do not rely on hardware mechanisms to enforce segregation. Developing a hardware-based Java Card Firewall implementation significantly enhances both security and performance.

Second, we proposed a JCVM memory layout [BGG21], labeled as (C3) in Figure 2.2. The JCVM memory layout is excluded from the Java Card specification and is typically implemented differently by each developer. To design a secure-oriented JCVM, it is necessary to have a reference implementation for each part of the JCVM to carefully evaluate and improve its robustness. Unfortunately, due to licensing restrictions associated to the Java Card specifications [Ora21a; Ora21b], the source code cannot be shared.

Future development of our JCVM implementation will need to enhance tamper resistance against hardware attacks, providing application developers, often not experts in hardware security, the necessary interfaces to protect their applications. Since Java Card 3.0.5, the introduction of the API SensitiveArrays and SensitiveResults classes have aimed to associate security properties with Java Card class variables. However, these classes are primarily implemented at the software level by the JCVM and lack reliance on underlying hardware security mechanisms. They currently support only specific Java Card types, which could be expanded through annotations, allowing developers to specify more precisely the expected security properties of their programs. These APIs currently offer only integrity protection, the inclusion of confidentiality is also crucial and should be considered in future revisions.

During Trouchkine's internship [Tro17], we explored the feasibility of running Java Card applications directly in a dedicated hardware environment. We modified an open-source Java processor [Sch05], capable of natively running Java bytecode, to execute Java Card bytecode while respecting its specific constraints. This approach improved performance and security by incorporating hardware security features directly into the Java Card runtime. This design enables the integration of hardware-based security with a strong execution platform, greatly enhancing overall security. Notably, commercial processors running Java bytecode as assembly language exist, such as Sun's Java Processor [Tur96], JStik by aJile Systems [Bin+08], and Arm microcontrollers with the Jazelle extension [Arm12]. Direct native execution of Java Card bytecode is not documented in the literature, highlighting the need for further research and development to maximize its potential.

#### 2.2.3.2 Perspectives in Hardware RoT Security

While SEs represent robust implementations of hardware RoT, there exist less secure implementations evaluated only for their hardware layer [Alb21]. A SE is a hardware RoT where both the hardware and software components have undergone a security evaluation. In contrast, a *secure-oriented microcontroller* is a hardware RoT where only the hardware has been evaluated. Secure-oriented microcontroller is commonly used in secure boot processes (see Figure 1.1a and Figure 1.1b) as the Google's Titan [BV21].

Emerging initiatives like the TrustedFirmware project [Leg23] aim to provide open-source software-oriented security to establish a CoT for COTS components. This project includes a bootloader based on MCUBoot, which offers firmware updates with signature verification and robust protections against hardware attacks for secure-oriented microcontrollers.

During Rosales's internship [Ros21], we conducted an analysis of MCUBoot under potential fault injection attacks, specifically focusing on how compilation parameters can influence the effectiveness of security countermeasures. The results of this work, presented by Arm [AG21] underlined the critical role of the compilation process in fortifying software against hardware attacks. It also emphasized the ongoing need for research to develop a secure RoT that substantially enhances the overall security framework of the CoT.

## 2.3 Security Analysis of the Input/Output Interfaces