### USING FUZZING APPROACH TO STRESS THE SECURITY OF ISO7816 COMMUNICATION PROTOCOL DRIVERS IMPLEMENTED IN SMARTCARDS

Internship feedback for graduation 16th June 2020

Boris SIMUNOVIC

GRENOBLE INSTITUTE OF TECHNOLOGY - ESISAR NATIONAL CYBERSECURITY AGENCY OF FRANCE

Company supervisors : Guillaume BOUFFARD and Eliane JAULMES Academic supervisor : David HELY

### INTERNSHIP FEEDBACK FOR GRADUATION

#### GRENOBLE-INP ESISAR 2017-2020

**Keywords:** cybersecurity, fuzzing, smartcards, ISO7816, embedded software development, software testing

**Abstract:** Smartcards are small electronic devices capable of processing and storing informations in a secure and tamper-resistant way. They are equipped with cutting-edge technologies to provide strong authentication and act as root-of-trust in bigger systems. These devices are ruling important and diverse interactions in our daily modern life by being for example involved in banking systems, telecommunications, public transportation and access control. In order to make sure those devices security mechanisms and countermeasures stay at the state-of-the-art, many governmental, industrial and academic research teams are working on this subject. In this internship a new method is proposed to asses the security and to benchmark the quality of the ISO7816 communication interfaces implemented as software executed on the card. This report describes a way to apply existing fuzz testing tools and methods to the smartcard specific case.

Mots clés: Cybersécurité, fuzzing, cartes à puce, ISO7816, développement sur cible embarquée, test logiciel

**Résumé:** Les cartes à puce sont des composants électroniques miniaturisés capables de traiter de l'information de maniere sécurisée. Ses caractéristiques en font une racine de confiance pour construire la sécurité à l'échelle d'un système complet, les rendant ainsi incontournables dans notre monde moderne et connecté. Nous pouvons mentionner, pour exemple, son utilisation dans les transactions bancaires, les télécommunications, les transports en commun et le contrôle d'accès.

Pour améliorer la sécurité de celles-ci, les cartes à puce alimentent de nombreux travaux de recherche. C'est dans ce cadre que ce projet propose une nouvelle méthodologie, sur la base des techniques de fuzzing, pour évaluer la sécurité des implémentations logicielles des interfaces de communication ISO7816 de ces cartes. Dans ce rapport, nous présentons une manière d'appliquer des outils de fuzzing existants et éprouvés au cas particulier des cartes à puce.

## Contents

| G        | Glossary 3                                |                                                           |                    |  |  |

|----------|-------------------------------------------|-----------------------------------------------------------|--------------------|--|--|

| 1        | $\begin{array}{c} 1.1 \\ 1.2 \end{array}$ | ject definition and goals<br>Introduction                 | <b>6</b><br>6<br>6 |  |  |

|          | $1.3 \\ 1.4$                              | Interest for smartcards and goals                         | $\frac{7}{7}$      |  |  |

|          | $1.4 \\ 1.5$                              | The attacker model                                        | 8                  |  |  |

|          | 1.6                                       | Discussing the open-source nature of the project          | 9                  |  |  |

| <b>2</b> | Intr                                      | coduction to smartcards and their communication protocols | 10                 |  |  |

|          | 2.1                                       | The need for a secure elements and a root of trust        | 10                 |  |  |

|          | 2.2                                       | What is a smartcard ? Definition and description          | 11                 |  |  |

|          | 2.3                                       | Electrical interface                                      | 12                 |  |  |

|          | 2.4                                       | Operating system structure                                | 13                 |  |  |

|          | $2.5 \\ 2.6$                              | The Application protocol data unit $(APDU)$               | $14 \\ 17$         |  |  |

|          | $\frac{2.0}{2.7}$                         | The ISO7816-3 T=0 communication protocol                  | 17                 |  |  |

|          | 2.1<br>2.8                                | Transmission of characters                                | $10 \\ 20$         |  |  |

| 3        | Intr                                      | roduction to fuzzing                                      | <b>22</b>          |  |  |

|          | 3.1                                       | Terms and definitions                                     | 22                 |  |  |

|          | 3.2                                       | The goal of the fuzzing algorithm                         | 23                 |  |  |

|          | 3.3                                       | A general fuzzing algorithm                               | 24                 |  |  |

|          | 3.4                                       | Taxonomy                                                  | 25                 |  |  |

| 4        | -                                         | -level engineering choices and strategy                   | <b>26</b>          |  |  |

|          | 4.1                                       | Fuzzing at the T=1 abstraction level                      | 26                 |  |  |

|          | 4.2                                       | Interfacing the targeted card with the fuzzer             | 26                 |  |  |

|          | 4.3                                       | Identifying interesting areas to be fuzzed                | 27                 |  |  |

| <b>5</b> |                                           | e bridge connector between the fuzzer and the smartcard   | 29                 |  |  |

|          | 5.1                                       | The smartcard communication interface                     | 29                 |  |  |

|          | 5.2<br>5.2                                | The computer communication interface                      | 30                 |  |  |

|          | $5.3 \\ 5.4$                              | The hardware running the bridge software                  | $30 \\ 32$         |  |  |

|          | $5.4 \\ 5.5$                              | The first, naive, strategy                                | 32<br>33           |  |  |

|          | 5.6                                       | Protocol state machine and its specificities              | $\frac{33}{34}$    |  |  |

|          | $5.0 \\ 5.7$                              | Development framework and toolchain                       | 39                 |  |  |

|          |                                           |                                                           | 50                 |  |  |

Internship Feedback

Fuzzing IS07816-3

| 8 | Con | clusion and further work               | 57 |

|---|-----|----------------------------------------|----|

| 7 | Res | ults                                   | 56 |

|   | 6.5 | Oracle definition                      | 54 |

|   | 6.4 | Communication protocol modelling       | 52 |

|   | 6.3 | Plugging the bridge to the fuzzer      | 47 |

|   | 6.2 | Boofuzz usage                          | 47 |

|   | 6.1 | Choosing the appropriate fuzzing tool  | 46 |

| 6 | The | fuzzing engine                         | 46 |

|   | 5.8 | Code verification and testing strategy | 40 |

|   |     |                                        |    |

# Glossary

| ACK     | Acknowledgment                                  |  |  |

|---------|-------------------------------------------------|--|--|

| AHB     | AMBA High-performance Bus                       |  |  |

| ANSI    | American National Standards Institute           |  |  |

| ANSSI   | Agence Nationale de la Sécurité des Systèmes    |  |  |

| 1111001 | d'Information - National Cybersecurity Agency   |  |  |

|         | of France                                       |  |  |

| APDU    | Application Protocol Data Unit                  |  |  |

| API     | Application Programming Interface               |  |  |

| ARM     | Advanced RISC Machine                           |  |  |

| ATR     | Answer To Reset                                 |  |  |

| CMSIS   | Cortex Microcontroller Software Interface       |  |  |

|         | Standard                                        |  |  |

| CPU     | Central Processing Unit                         |  |  |

| EEPROM  | Electrically Erasable Programmable Read-Only    |  |  |

|         | Memory                                          |  |  |

| ESN     | Electronic Serial Number                        |  |  |

| ETU     | Elementary Time Unit                            |  |  |

| FIFO    | First In First Out                              |  |  |

| FTP     | File Transfer Protocol                          |  |  |

| GDB     | GNU Debugger                                    |  |  |

| GNU     | GNU's Not Unix!                                 |  |  |

| GPL     | GNU General Public License                      |  |  |

| GT      | Guard Time                                      |  |  |

| HAL     | Hardware Abstraction Layer                      |  |  |

| IDE     | Integrated Development Environment              |  |  |

| IP      | Internet Protocol                               |  |  |

| JTAG    | Joint Test Action Group                         |  |  |

| JVM     | Java Virtual Machine                            |  |  |

| LRC     | LRC Longitudinal Redundancy Check               |  |  |

| LSC     | Laboratoire de la Sécurité des Composants -     |  |  |

|         | Hardware Security Lab                           |  |  |

| MSISDN  | Mobile Station Integrated Services Digital Net- |  |  |

|         | work                                            |  |  |

| NFC     | Near Field Communication                        |  |  |

| OIV     | Opérateur d'Importance Vitale                   |  |  |

| OSI     | Open Systems Interconnection model              |  |  |

| RAM     | Random-Access Memory                            |  |  |

| ROM     | Read-Only Memory                                |  |  |

|         |                                                 |  |  |

### Fuzzing IS07816-3

### Internship Feedback

| SDE   | Sous-Direction Expertise - Expertise Depart-      |  |

|-------|---------------------------------------------------|--|

|       | ment                                              |  |

| SGDSN | Secrétariat Général de la Défense et de la Sécur- |  |

|       | ité Nationale                                     |  |

| SIM   | M Subscriber Identity Module                      |  |

| TACS  | Total Access Communication System                 |  |

| TCG   | TCG Trusted Computing Group                       |  |

| TCP   | Transmission Control Protocol                     |  |

| TPDU  | Transmission Protocol Data Unit                   |  |

| TRNG  | True Random Number Generator                      |  |

| UART  | Universal Asynchronous Receiver-Transmitter       |  |

| UML   | Unified Modeling Language                         |  |

| USB   | Universal Serial Bus                              |  |

| WT    | Wait Time                                         |  |

## Remerciements

Je souhaite profiter de ce rapport de stage qui clôture mes études universitaires pour remercier les personnes qui m'ont entouré durant ma formation d'ingénieur, à l'école comme en entreprise.

Je pense tout particulièrement au laboratoire de la sécurité des composants de l'ANSSI, à Eliane Jaulmes et Guillaume Bouffard, mes encadrants, pour m'avoir fait confiance et avoir choisi de m'intégrer dans l'équipe comme leur premier apprenti.

J'y ai côtoyé durant trois ans des collègues formidables qui ont montré énormément de patience et de bienveillance, qui se sont montrés tout particulièrement disponibles pour échanger aussi bien à propos de mon projet qu'à propos de leurs propres activités de recherche. Des personnes passionnées qui m'ont donné le goût pour des disciplines variées telles que l'analyse side-channel, les attaques en fautes, la cryptographie, les statistiques, l'intelligence artificielle, l'architecture des processeurs, les cartes à puce et la sécurité des logiciels embarqués. Je pense à mes encadrants, mais également à Adrian Thillard, Louiza Khati, Emmanuel Prouff, Ryad Benadjila, David El Baze, Thomas Trouchkine et Karim Khalfallah.

Je veux remercier mes enseignants de l'Esisar ainsi que mon tuteur académique David Hely. J'ai fréquenté cette école durant cinq années mémorables, j'y ai rencontré de bons amis, et aussi des professeurs qui m'ont marqués, qui m'ont transmis leurs connaissances et qui m'ont servi d'exemple. Je pense aussi au personnel de la scolarité et aux enseignants qui m'ont soutenu dans des moments difficiles, notamment Nathalie Fulget, Nicolas Charroud, Romain Siragusa, David Hely et Mylène Chavarot, mais aussi la Fondation Grenoble-INP, en particulier Murielle Brachotte.

Je souhaite également remercier mes parents pour m'avoir transmis le goût de l'effort et cette avidité de comprendre les choses qui m'entourent. Pour finir, je remercie les personnes m'ayant aidé dans la relecture de ce rapport, notamment Jean Bonnevie, Christopher Lievin, Emeline Leveaux, Mehdi Hidri, Guillaume Bruchon, Benoit Etcheberry ainsi que mes encadrants.

## Chapter 1

## Project definition and goals

### 1.1 Introduction

This report is closing a three years period of education at the Grenoble national institute of technology and of apprenticeship at the national cybersecurity agency of France to obtain the engineering degree. This document goes back on three years of skills upgrading about the smartcards subject and presents the final internship project consisting in fuzzing smartcards communication interfaces.

First chapters of this report aim to explain project stakes and context and to settle all the necessary background information to understand the problematic and proposed solutions. Especially, it will bring a particular attention to the definition of a smartcard and its communication protocols. In a similar way it will go through the concept of fuzzing, explain why this methodology is relevant to the given situation. Subsequent chapters demonstrate the technical solutions developed during the internship to apply fuzzing discipline to smartcards and finally, results are presented and next steps for further work are identified.

### 1.2 The French national cybersecurity agency and its research facilities

The two latest defence white papers ordered in 2008[3] and 2013[4] by the French presidents Nicolas Sarkozy and Francois Hollande are both mentioning the strategic aspects around cybersecurity. It is clearly stated as a priority in the next years for the sovereignty and security of the nation. The politics and decision makers are advised to invest the resources to develop the trust, reliability and the security in the systems of informations. As a result of these politics the National Cybersecurity Agency of France (ANSSI) was created in 2009 and was given a great power to coordinate all the efforts in cybersecurity on a country-wide scale.

ANSSI is part of the General Secretariat for Defence and National Security (SGDSN), an interministerial body placed under the authority of the French Prime Minister which "assists the head of government in designing and implementing security and defence policies" [2]. The agency was given various missions

including anticipation of the threats against systems of information, defence of governmental infrastructures and networks, protection of the vital operators (OIV), pro-active response to cybersecurity issues, coordination between state entities, enhancing security awareness and education[6].

The internship takes place in the expertise department (SDE) of the agency. It is mainly structured as an aggregation of research laboratories. The goal is to have teams of researchers who are permanently at the state-of-the-art on critical designated subjects to be able to provide expertise to other departments or entities. They are also given the mission to stimulate and orient the academic and industrial research in their respective areas at the scale of France and international community. The research efforts led by the agency are often published in academic conferences and journals which enables peer reviews by the international scientific community, thus reinforcing the scientific grounding and credibility of the work accomplished by the agency. This also provides scientific references to the industrial partners[5] and helps to improve the overall security by making the informations widespread and publicly available.

More precisely, the internship takes place in the hardware security lab (LSC) whose work aims to improve the security of hardware components like cryptographic accelerators, secure elements and processors against a wide range of physical attacks like side-channel and fault attacks and keep protected critical assets like encryption keys.

### **1.3** Interest for smartcards and goals

Smartcards are small physical components with the ability to communicate, store and process data. They usually aim to provide secure and tamper-resistant storage to protect cryptographic assets and strong security primitives like cryptographic accelerators. As they are designed solely for this purpose, they are often part of a bigger system and act as a root of trust. Smartcard characteristics are going to be discussed in depth in Section 2. Given its wide spread, its critical position inside systems and its hardware nature, it naturally falls in the field of interest of the hardware security research lab (LSC).

This project is focused on the communication ability of the device. It is the natural way to interact with the card, to execute commands on the card and to access informations. Thus, it could be one of the biggest and most straightforward entry-point for a potential attacker, its implementation has to be very secure, robust and the protocol specifications have to be strictly followed. This research project aims to find new ways to asses the security level of the software implementations of the communications drivers in current card implementations.

### 1.4 The functional needs

The smartcards have several standardized ways to communicate with the outside world. The two most popular ones are the wireless protocol defined by the ISO14443[9] using a close to NFC technology and the second one, the most deployed one is the wired protocol defined by the ISO7816[12] standard. In this project, we focus on the ISO7816 protocol detailed in Section 2.

The goal is to develop a methodology and tools to be able to assert the quality

of the software implementation of the ISO7816 protocol of any smartcard. The approach has to be automatable and reproducible. The developed tool has to stress the implementation of the protocol to asses how well it is compliant with the specifications and especially how well it defends itself against atypical and malformed inputs. The tool has to produce reliable, interpretable and comparable metrics in order to be able to take decisions about the quality of the driver. It is also expected to detect when an input produces unexpected behaviour and gather all the necessary diagnostic informations to reproduce it and fix it.

### 1.5 The attacker model

When dealing with security, it is often important to make a model of the opponent, especially how powerful he is, how much resources he can invest, how much informations about the target he can access. The goal is to identify and categorize its abilities. This model is then used to design the system and to introduce the proper countermeasures. A very common way to categorize an attacker is focusing on how well he is informed about the target. How much information he can have about the design of the target and how much informations he can access during the runtime of the device. People mainly agree on three categories.

The first one is the white-box model with the highest assumptions on the opponent. In this scenario, the attacker has all the informations he wants about the target, he has access to all the datasheets and he can instrument the target, gather a lot of informations about its internals during the runtime of the target device. The attacker has a clear view of the design and of what is happening inside the target. As the assumptions are the highest, the attacks considered in this model are potentially the most sophisticated and powerful and they give the best appreciation of the security level.

The second one is the black-box model with the lowest assumptions about the knowledge of the attacker. It is assumed that the attacker has no informations about the design and about what is going on inside the target. He is only aware of the input applied to the "black-box" and its output.

There is an intermediate grey-box model. In this case, the attacker is supposed to have partial informations about the design and he is able to obtain some intermediate computation results or measure some side-effects.

Nowadays from a designer point of view, in extension to the Kerckhoffs rules[13], the approach is usually to make the higher assumptions about the attacker and to design the security as if the attacker knew everything about the target. The system is then called "secured by design", the developer does as if the design was publicly available, the security is brought by a smart design itself rather than by opacity. This is a relatively new approach in hardware design and it is opposed (and has proven to be better) to the old scheme of security by opacity where security is broken from the moment the attacker access critical informations (through social engineering for example), thus breaking the designers assumptions about the attacker.

From the attacker point of view, the tendency is rather to make less assumptions about the information it can access, thus he can make his attack scenario more general and less dependent on sometimes hard to get or expensive information. Given the very limited access to smartcards applications and operating system and the very restricted access to documentation, the black-box model was naturally chosen in order to stay coherent with the open-sourcing goal. This is a way to check the results an attacker could obtain even if he knows nothing about the target.

### 1.6 Discussing the open-source nature of the project

The project is meant to be open-sourced. The long-term goal is to make the code, the documentation, the design and the tools freely and widely available to the academic community, the industrials, the citizens and the certification and governmental bodies. Everyone has to be able to build the tool, use it, modify it and contribute. Thus, this project will contribute to improve the academic state-of-the-art in this discipline, it provides tools to the designers and certifications bodies to stress the security of their implementations. It enables the clients to tests on their own the quality of the products they are buying and it compels the industrials to produce devices which are resilient to state-of-the-art attacks with publicly available tools. From the overall point of view and from the citizen point of view, it brings more transparency and a greater trust into the targeted systems.

From a project management point of view, open-sourcing is a way to leverage more resources by interesting other people in order to contribute and make the project go further. It ensures more sustainability by having more people working on it from several entities and companies. It is not dependent on a single team or a single person who can leave the company. It also introduces a way of working proper to collaborative open-sources projects like rigorous methods of versioning and of documentation writing.

### Chapter 2

# Introduction to smartcards and their communication protocols

# 2.1 The need for a secure elements and a root of trust

Before giving the functional and physical definition of a smartcard in Section 2.2, they are several examples to explain how came the need for such components. This helps to understand the criticality of those devices and the reason why the LSC is focusing on this important field of research. The purpose of this section is to go through the examples of the mobile telephony and of the banking systems in order to make the reader to understand the role the smartcards are playing in overall systems.

In the early 1980s, one of the first mobile phone systems was in use in the United Kingdom. It was called TACS standing for "Total Access Communication System"[8] and it was a pretty good achievement with the technologies of its time so the focus was not really on the security and the confidentiality. The authentication of the user on the network was quite simple. The mobile handset was storing two numbers in its internal memory. The first one, the Mobile Station ISDN number (MSISDN) is more or less equivalent to nowadays phone number, it is used to dial with a specific user. The second one, the Electronic Serial Number (ESN), is a unique identifier for the handset. During the authentication process, the phone was sending over the network the two numbers, the network was then comparing the received pair with the ones stored in its central database. If the ESN serial number of the phone was matching the MSISDN number it is supposed to be attached to, then the access was granted and the handset authenticated over the network. The security stopped so far. There was no encryption process to ensure the confidentiality of the MSISDN and ESN identifiers being sent on the network and no software or hardware mechanism to prevent somebody (not being the service provider) from re-writing those numbers in the internal memory. It was then possible for a third-party to eavesdrop the authentication process, to steal the two numbers and write them inside their

own phone and then usurp the identity of the victim and do phone calls for free. In the previously described case, there are several noticeable issues : the user of the handset can not be trusted, there is a need to have a secure piece of memory with read and write operations protected from an unauthorized person. It has to be protected against physical means and software attacks. There is also a need for cryptographic primitives to provide encryption. Those observations conducted to the usage of *SIM* cards which are smartcards. In the banking environment, similar situation are encountered with the credit cards. There is a need to securely store the customer identifiers and prevent a third-party to steal and copy signature keys. Globally, there is a need for a secure component providing security primitive in order to build an overall trust in the system.

### 2.2 What is a smartcard ? Definition and description

As the form-factor of a smartcard can vary, its functional definition is more relevant in the case of this project. In [8], it is defined as an object which :

- 1. can participate in an automated electronic transaction

- 2. is used primarly to add security

- 3. it is not easily forged or copied

- 4. can store data securely

- 5. can host/run a range of security algorithms and functions

Every computer system is built with multiple levels of abstraction and generally, higher layers must trust lower layers. The initial source of trust is called the root of trust[15]. The Trusted Computing Group (TCG) encourage building secure systems with a "physically secure trusted component that can be used as a foundation upon which trust in the rest of the system can be built"[8, p. 157]. All the entities in the overall system interact with this secure module and can thus be given a good level of insurance that it is behaving as expected. The smartcards, with the functional description aforementioned, are designed to provide this root of trust.

A smartcard is typically composed of a few square milimeter large piece of silicon embodied in a piece of plastic shaped as a card as depicted in Figure 2.1. It contains a microcontroller able to process information, cryptographic accelerators, TRNG and memories like ROM, NVM and RAM. It is also provided with metallic connectors to be able to communicate with an external card reader via the ISO7816 protocol described further in Sections 2.6 and 2.7. It eventually embodies an antenna for NFC communication using the ISO14443 protocol. The shape and physical characteristics of the card are standardized in ISO7816-2[11]. When dealing with the wired communication, the electrical characteristics and low level communication protocols are defined in the ISO7816-3[12]. Then, the ISO7816-4 standard gives a functional description of the application level communication protocol used both in wired and NFC communications. It is based on the APDUs described in Section 2.5.

In both contact and contact-less modes, the card interacts with a reader device. Its role is to provide power and clock to the card and initiate the

Figure 2.1: Typical smartcard shape with its contacts for providing ISO7816 communication. Klipe / CC BY-SA (https://creativecommons.org/licenses/by-sa/4.0)

transactions. It typically request the card to read or write informations and execute actions like a cryptographic computation. The card can be compared to a web server[1, p. 21], it reacts on requests, stores and serves the information requested by the reader while making sure that the information are served to a strongly authenticated user.

### 2.3 Electrical interface

When using the wired communication protocol, the card is connected to the reader by the metallic contacts depicted in yellow on Figure 2.1. This connector is composed of several pins detailed on Figure 2.2 and their purpose is defined in the ISO7816-3 standard[12].

The pin C5 (GND) is used to share a common ground, a reference electric potential, across the reader and the card. It is used for both the power supply and the communication. As long as the card is powered by the reader, the pin C1 (VCC) is used to provide power supply to the card. Depending on the use-case it can be 1.8V, 3V or 5V. The card does not have its own clock source, the reader is in charge of providing the common time source through the C3 (CLK) input pin. It is specified to vary and take any value between 1MHz and 5MHz. The C2 (RST) is an input pin used by the reader to send a reset signal to the card. The C7 (I/O) pin is the data transmission line used to exchange informations with the protocols described in Sections 2.6 and 2.7. It is both an input and an output because the communication protocol is half-duplex. All the other pins are reserved either for future use or for proprietary use.

Figure 2.2: Smartcard ISO7816-3 connector pinout. Dacs, WhiteTimberwolf / CC BY-SA (https://creativecommons.org/licenses/by-sa/3.0)

### 2.4 Operating system structure

To provide all the functionalities described in Section 2.2, the microcontroller inside the card is running various pieces of software. Figure 2.3 gives a top-level view of the different software layers of abstraction on a JavaCard technology smartcard. First of all, the chip manufacturer provides a hardware abstraction layer (HAL) with the microcontroller. This piece of software eases the access to the hardware resources (like for eg. the UART/ISO7816 interface). It theoretically also makes the following layers independent from the underlying hardware. Then, on the top of the HAL, there is an operating system in charge of managing the physical resources like memory and CPU time. It is also in charge of dealing with the ISO7816-3 communication interface via a dedicated driver. It then exposes this service to the upon applications via a system API. Depending on the implementation, this driver is usually executed in the kernel space. It could be partially or not isolated. This makes it critical from a security point of view, so this is the main part of code whose security has to be stressed with the fuzzing approach. Then, on the top of this operating system, usually runs a Java virtual machine (JVM) which emulates the java instruction set to run multiple java applets and ensuring java security policies. On the top of the operating system and the JVM are running one or more Java applets, computer programs defining the behaviour of the smartcard. Depending on the use-case, those can be loaded in by the manufacturer, the card issuer or the user.

According to the attacker model defined in Section 1.5, in the frame of this project, there is no access to the operating system to get informations about how the driver under test behaves, no access to any logs or internal system administration tools. Nor is it possible to have an accomplice applet on the target.

Figure 2.3: Top-level software architecture of the smartcard using te JavaCard technology.

### 2.5 The Application protocol data unit (APDU)

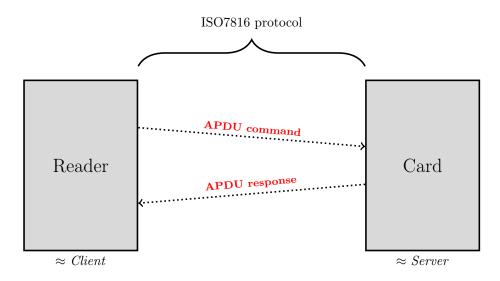

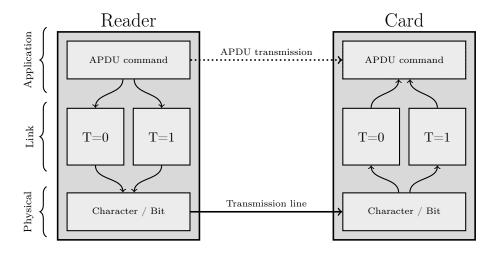

The communication between the reader and the card is organized upon several layers. Each layer brings a new service and a new abstraction level. The top-level most abstracted unit described by the ISO7816 is the Application Data Protocol Unit (*APDU*). It can be compared to the "application layer" described in the well known *OSI* model[10]. It directly carries application data and operations to be executed by the card. These can be intended to the operating systems, for example for file system management and system administration or can be intended as well to specific applets running on the card. It is organized as a client-server model, where the card reader sends requests and commands to the card whose role is to respond, serve information and execute the requested actions.

An APDU is a well defined data structure organized as a sequence of bytes. It can be represented as a frame like described in Figures 2.5 and 2.6. There are two kinds of APDUs: the APDU commands and the APDU responses. As shown in Figure 2.4, the reader is always initiating the communication asking the card to do something by sending an APDU command. Then, the card is supposed to give an answer in the form of an APDU response. The roles can not be inverted.

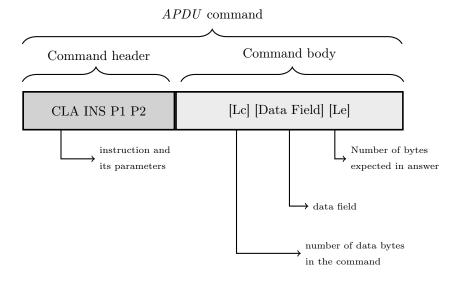

The *APDU* command (illustrated in Figure 2.5) is composed of a mandatory header and a optional body. Structure and size of the header can not vary, it is always composed of four fields of information designated by the names : CLA,

Figure 2.4: Illustration of a typical APDU transaction. The reader sends an APDU command to the card. The card answers back with an APDU response.

INS, P1 and P2. The CLA byte carries information about the class of the instruction. INS is a byte coding for the instruction itself, it corresponds to the action to be executed by the operating system. For example running an applet or getting the content of a file. P1 and P2 bytes contain the operands and options associated to the previous INS byte. Then, the body is composed of the Lc, Le and data bytes from Figure 2.5, they are all optional. Lc can be one or two bytes and it encodes the number of data bytes carried in the following data field of the APDU command. Le can also be one or two bytes, it encodes the number of data bytes command.

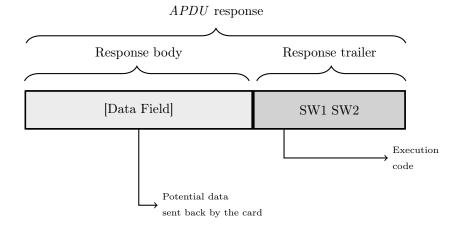

The APDU response illustrated in Figure 2.6 is sent by the card when it has finished to process the previously sent command. It is first composed of an optional body eventually containing data returned by the card. It is then followed by a mandatory two bytes trailer. These bytes called SW1 and SW2 encode an execution code indicating the status of the card, it usually says if the command was processed correctly or if an error has occurred.

The bytes of information composing the APDU command are not directly pushed in the transmission line. This is only a conceptual abstract object from the application layer, it is not understandable by the physical components in charge of emission and reception of bits. It has to go through several intermediate steps in order to serialize the data and deal with the reality of the physical transmission line. This is partially the purpose of the underlying link layer protocol which encapsulates the bytes of information from the APDU. Smartcards have the particularity that the ISO7816-3 standard defines two different protocols to do the same task as pictured on Figure 2.7. They are respectively called the T=0 and T=1 protocols, they are both discussed in Section 2.6 and Section 2.7.

Figure 2.5: Illustration of the APDU command structure

Figure 2.6: Illustration of the APDU response structure

16

Internship Feedback

Fuzzing IS07816-3

Figure 2.7: ISO7816 protocol is built upon several abstraction layers of abstraction. The APDU objects can be carried by either the T=0 and T=1 underlying protocols.

### 2.6 The ISO7816-3 T=0 communication protocol

The aim of this section is to briefly discuss T=0 protocol. This protocol can be roughly compared to the "link layer" defined in the well known  $OSI \mod[10]$ even if in practice the isolation of this layer from the other ones is not very strong. Its purpose is to enable the transmission of the APDU abstract object over the transmission line.

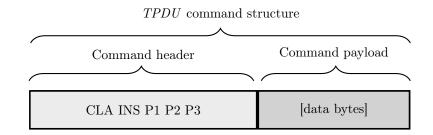

This protocol operates by decomposing the APDU object into intermediate structures called TPDU commands. As illustrated in Figure 2.8, the TPDUcan be respresented as a sequence of bytes. Its header is a sequence of five bytes CLA, INS, P1, P2 and P3. The four first ones are matched on CLA, INS, P1 and P2 from the related APDU structure defined in Section 2.5. P3 byte is used to encode the number of data to be transferred during the command.

There are different scenarios depending on the Lc and Le values defined in Section 2.5 of the APDU structure. The exchange of TPDUs between the reader and the card is not going to be the same depending whether data have to

Figure 2.8: Illustration of the TPDU command structure. CLA, INS P1 and P2 are same as the APDU defined in Section 2.5. P3 encodes the number of data bytes.

| Case 1  | No command data field       | No response data field       |

|---------|-----------------------------|------------------------------|

| Case 2  | No command data field       | Response data field          |

| Case 3  | Command data field          | No response data field       |

| Case 4  | Command data field          | Response data field          |

| Case 2E | No command data field       | Extended response data field |

| Case 3E | Extended command data field | No response data field       |

| Case 4E | Extended command data field | Extended response data field |

Figure 2.9: The four structures of command APDUs.

be sent to the card or not and depending whether data are going to be expected back from the card, how many data are expected, if both entities agree on the amount of data etc... The possible scenarios are detailed in Figure 2.9. Usually several *TPDU* commands and responses are exchanged between the reader and the card to process a single *APDU*. Typically in the case 4 from Figure 2.9 (where the processing of the *APDU* command requires to send data bytes in the direction of the card and then to get back data bytes from the card as a response), a first *TPDU* is sent with the original command described in the related *APDU* (CLA, INS...), with the data bytes which have to be sent, then, when the card is ready, the reader sends another *TPDU* command to request the answer from the card. The sequence of bytes fixed by the T=0 protocol goes through the physical layer detailled in Section 2.8.

The reader first initiates the transaction by sending the first five bytes of the header in a row. Then it waits for the card to answer back a so called "procedure byte". It can be one of the four subsequent possibilities :

- 0x60, is a null byte, it tells the reader device the card needs more time to process the instruction. It resets the timeout counter.

- 0x6x or 0x9x is an *APDU* response SW1 byte as defined in Section 2.5. The reader is then supposed to continue to listen to receive the subsequent SW2 byte.

- The same INS as the previous TPDU header (as defined in Figure 2.8). It is an ACK byte, the reader is expected to send all the TPDU data bytes in a row.

- The same INS as the previous *TPDU* header xored with 0xFF is an *ACK* byte. The reader is expected to send only the next byte of the data field and then to wait for another procedure byte.

### 2.7 The ISO7816-3 T=1 communication protocol

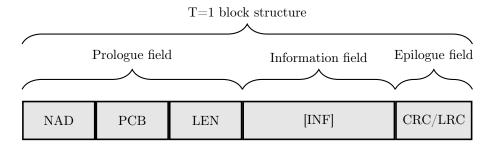

The T=1 protocol was designed to replace T=0 by bringing some improvements, however T=0 is still largely in use nowadays. T=1 protocol is designed to fulfil the same (link layer) functional needs than T=0 (detailed in Section 2.6), however it is designed to improve some lacks in the previous protocol, especially the isolation between the abstraction levels of the protocol stack. It makes a clear distinction between the physical layer, the link layer and the application layer. It is block oriented and improves error correction capacity. For the reasons

Figure 2.10: Illustration of a T=1 protocol block as defined in ISO7816-3[12]. The block is composed of two madatory fields : epilogue and prologue and one optionnal field : data. NAD, PCB and LEN are one byte long each. CRC/LRC is on or two bytes depending on the checksum algorithm. Data field is up to 254 bytes.

exposed later in Section 4.1, the security testing efforts of this project are going to be focused on that part of the ISO7816 protocol.

T=1 protocol is block oriented, that is, the APDU structure described in Section 2.5 is cut in few bytes pieces which are then encapsulated in T=1 block structures illustrated in Figure 2.10. This block structure is composed of three byte fields : the prologue field, the information field and the epilogue field. The prologue is a three bytes long mandatory field, it carries control informations and metadata about the content of the block. The Node Address byte (NAD) is used in the case of several devices on the same shared bus and is an advanced functionality of the protocol. The Protocol Control Byte (PCB) encodes informations required to control the transmission, especially the "type" of the current block among the three following possibilities :

- I-Block, meant to carry a payload composed of data bytes corresponding to pieces of *APDU*s.

- R-Block, used as acknowledgement or error signaling.

- S-Block designed to negotiate communication parameters between the reader and the card.

The LEN byte purpose is to encode the length of the subsequent information field between 0 and 254. The information field is designed to carry the payload encapsulated inside the current block (upper layer protocol data). The block finally ends with a correction code, it can be one or two bytes long depending on the kind of error detection/correction currently in use. It can be either Longitudinal Redundancy Code (1 byte LRC) or Cyclic Redundancy Code (2 bytes long CRC).

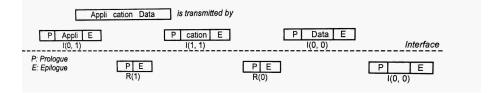

I-Blocks are used to carry informations and data. If the maximum size of the block is not enough to fit all the data bytes, then several blocks have to be sent in a so called "chaining process". For this purpose, the I-Block PCB contains a "sequence number bit" counting (modulo two) the sequence number of the current block. It contains as well a "more data bit" used to indicate to the other device that there is more data to be transmitted, and so, this is not the last I-Block. After the reception of a chained I-Block, the device uses an

Figure 2.11: Illustration of the chaining process taken from the ISO7816-3[12] standard. It represents the "application data" frame being split in three distinct blocks. I(M, S) is for an I-Block with more data bit M and sequence number S. R(S) is for an R-Block requesting the I-Block with sequence number S.

R-Block to acknowledge it and to request the next one by explicitly indicating the requested sequence number in the R-Block structure.

R-Blocks don't carry any information field, they are sent as a response to a previous block. They are used to acknowledge it or to ask the next one. If something went wrong, for example a CRC error or wrong sequence number received, their aim is to request again the block with the expected sequence number. In their PCB, they carry a sequence number bit for this purpose.

S-Blocks are used to re-negotiate T=1 communication parameters. There is the four following kinds of S-Blocks and they can be sent either by the reader and the card. Each of them exists in its request form and its response form. One device initiates the negotiation by sending an S-Block request, then the other device can either acknowledge it or refuse by sending back an S-Block response. S-Blocks eventually contain a 1 byte long information field encoding the requested value for the parameter :

- IFS request and IFS response : is used in order to negotiate the maximum size (in number of bytes) of the I-Blocks information fields.

- WTX request and WTX response : is used in order to negotiate timeout value in between blocks.

- RESYNCH request and RESYNCH response : after several protocol errors (like non-acknowledgement, wrong sequence numbers etc...) a device can request a resynchronization, the protocol state machine goes back to a known state.

- ABORT request and ABORT response : if after several errors and resynchronisation attempts there is no improvements, then a device can request to completely abort the transaction with this block.

### 2.8 Transmission of characters

In the  $OSI \mod[10]$  the "physical layer" corresponds here to the transmission of characters/bytes and bits on the transmission line (I/O pin C7 from Section 2.3). The ISO7816-3 standard describes how to transmit a character in the I/O line, it is quite similar to the standard UART protocol with some differences which are going to be discussed in this section.

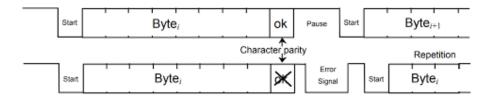

Figure 2.12: Illustration of a character frame taken from the ISO7816-3 standard[12]. It is possible to see the ten moments composing the character frame, the guard time and the error signal.

First of all, it is not exactly asynchronous because there is a shared clock across the two devices via the pin C3-CLK (see 2.3), the two devices agree on an elementary time unit (ETU) which is a multiple of the shared clock period. This number of ETU per second is equivalent to the baudrate in UART protocol. A character is composed of 10 moments followed by a pause time as depicted in Figure 2.12. A moment is defined as a 1 ETU period of time where the I/O line is either at the state high or low. The pause time is defined as a several ETUtime period where the reader remains in reception mode. The first moment is a start bit, the I/O line should be pulled to low state by the reader. Then, the next 8 moments are coding for the byte of data to be sent. The 10th moment is defined to be a parity bit to enable some basic error detection. After the last moment the reader should remain in the pause state during at least two ETU. This pause can be used by the other device to pull the I/O line to low state to signal an error, the character is then sent again. The standard also defines a guard time (GT) and a wait time (WT) and constrains on the time precision of the ETUs. The GT is a minimum delay to be respected between the leading edges of two consecutive characters and WT is the maximum delay between the leading edges of two consecutive characters. It allows to detect an unresponsive card.

Another big difference is that the communication is half-duplex, both the card and the reader are using the same transmission line to emit characters. It is assumed that (because of the higher level protocols described in Section 2.6 and Section 2.7) both devices know when it is their time to emit a character, so no collision should happen. Thus, there is no need for an medium access management protocol.

## Chapter 3

## Introduction to fuzzing

Fuzzing is a software testing discipline, meaning it is a set of methods aimed to help increase the level of insurance that a particular piece of software is behaving as it was specified to. These tests are not specifically security oriented, it could be used to test performances like execution time and memory usage to identify situations where computer resources are used in an abnormal way while other kinds of tests aim to make sure the outputs provided by the tested software are those specified by the functional needs. Finally, it is also used to check if the target is resilient to malicious inputs aimed to trigger non intended behaviours. This project is mainly focused around the two last points. Fuzzing mainly differs from conventional testing by the fact that the test routines are not hand written accordingly to a specification, they are rather automatically generated and checked by an algorithm. The purpose of this section is to introduce the reader to fuzzing methodology and to settle down the necessary vocabulary and background information.

### 3.1 Terms and definitions

In the fuzzing literature and in the very numerous available tools, the involved terms are quite diverse and heterogeneous. This Section defines the most important vocabulary to describe the fuzzing process mainly accordingly to [14].

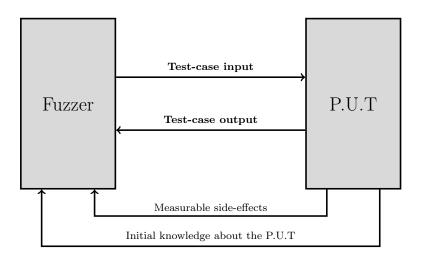

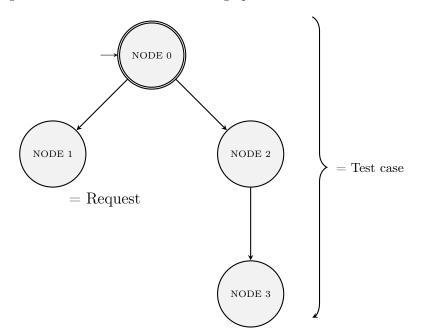

The Program Under Test (P.U.T) is the software implementation currently being tested, it is represented on the right side in Figure 3.1. Fuzzer is another entity external to the P.U.T represented on the left side, it performs the fuzz testing (or fuzzing) by interacting with the P.U.T by applying inputs. Fuzzer has access to the program output and depending on the attacker model (discussed in Section 3.4) it can eventually have an embedded knowledge about target implementation or access information about program execution. Then, "*Fuzzing* is the execution of the P.U.T using input(s) sampled from an input space (the "fuzz input space") that protrudes the expected input space of the P.U.T"[14]. This means that the "fuzz input space" is not equal to the initially specified or expected input space. The generated inputs can be a part of the expected input space but could also be out-of-specification, malformed and unexpected inputs which may be processed incorrectly and may trigger unintended behaviours. A test-case is one element taken from the "fuzz input space" which is going to be

Figure 3.1: Illustration of the interactions between the fuzzer and the P.U.T (Program Under Test).

applied to the P.U.T. The fuzzing algorithm detailed in Section 3.3 sequentially chooses test-cases in the "fuzz input space", applies them to the P.U.T in a process called a fuzz iteration. The bug oracle is the part of the fuzzer in charge of discriminating on the basis of the feedback informations if such an unintended behaviour happened. The fuzz configuration is a set of parameters controlling fuzzer execution, it is mainly composed of informations and description about the input space. Different ways of describing it are presented later in Section 3.4.

### 3.2 The goal of the fuzzing algorithm

Typically the fuzz input space depicted in Section 3.1 is extremely large or even infinite. Naive fuzzer implementations randomly sample this space. It is not really efficient because the number of fuzz iterations achievable in a reasonable finite time is not significant compared to the space size. A smarter fuzzing process would rather implement a strategy to bring out the most promising test-cases and try them first. Most of state-of-the-art implementations can be compared to an optimisation problem. First, the operator chooses a metric correlated with the goal he wants to achieve, it could be for example a code coverage ratio, the number of conditional branchments looked over or the number of unit bugs found. Then, the fuzz algorithm goal is to try to browse the fuzz input space in such a way that it maximises or minimizes this metric. Choice of the metric is decisive, each of them has advantages and counterparts. For example, a lot of available fuzzing tools are using code coverage which is easy to compute but not always relevant because it gives the same weight to benign portions of code and to critical ones. It also easily sticks into a local maximum. Most sophisticated fuzzers implements evolutionary algorithms [14], machine learning and deep learning methods<sup>[7]</sup> to learn in real time how the P.U.T reacts and which test-case should be chosen next. Quality of the metric and of the optimisation is directly correlated to the amount of available informations about

16th June 2020

Page 23/59

P.U.T execution and to the attacker model.

### 3.3 A general fuzzing algorithm

```

Input: \mathbb{C}, t_{limit}

1

Output: \mathbb{B} // a finite set of bugs

2

3

\mathbb{B} \leftarrow \emptyset

4

\mathbb{C} \leftarrow \operatorname{Preprocess}(\mathbb{C})

\mathbf{5}

6

while t_{elapsed} < t_{limit} \land CONTINUE(\mathbb{C}) do

7

conf \leftarrow \text{Schedule}(\mathbb{C}, t_{elapsed}, t_{limit})

8

tcs \leftarrow InputGen(conf)

9

// O_{bug} is embedded in a fuzzer

10

\mathbb{B}', exectinfos \leftarrow \text{INPUTEVAL}(conf, tcs, O_{bug})

11

\mathbb{C} \leftarrow \text{ConfUpdate}(\mathbb{C}, conf, execinf os)

12

\mathbb{B} \leftarrow \mathbb{B} \cup \mathbb{B}'

13

14

return \mathbb{B}

15

```

In [14] is presented a fuzzing algorithm which generalizes well most of the existing fuzzing processes and helps to understand the method implemented in this project. It is presented in Figure 3.2 and takes as arguments a fuzzing configuration  $\mathbb{C}$ , a finite time bound  $t_{limit}$  and outputs a set of bugs  $\mathbb{B}$ .

The PREPROCESS() instruction at line 5 is in charge of preprocessing the fuzz configuration  $\mathbb{C}$ . Typically it analyses the description of the input space and tries to minimize it to save execution time. Depending on the scenario and the attacker model this instruction also instruments the code to be able in the next steps to gather feedback information about P.U.T execution.

Then, at line 7 the fuzzing process itself starts and runs until the time limit is reached or until the CONTINUE() function decides on the basis of the configuration data to stop the process. Each execution of the content of this loop is called a fuzz iteration.

At line 8, the SCHEDULE() function takes as parameters information about the current fuzz iteration and the global configuration  $\mathbb{C}$ . It outputs the configuration *conf* to be applied for the current fuzz iteration.

The INPUTGEN() function at line 9 takes as a parameters the current fuzz iteration configuration conf and builds tcs, the concrete test-case to be applied as inputs to the P.U.T.

At line 11, the INPUTEVAL() function takes as parameters conf, tcs and a bug oracle  $O_{bug}$  and applies the test-case to the P.U.T. On the basis of  $O_{bug}$ , the function decides if the execution went well or not and eventually returns found bug  $\mathbb{B}'$ . It is also in charge of gathering information about the current execution : *execinfos*, to be able to optimize in real-time to fuzzing process. Finally, CONFUPDATE() function at line 12 uses the gathered feedback information about the current fuzz iteration to optimize the fuzzing process, especially the input space browsing, by updating the global configuration  $\mathbb{C}$ .

### 3.4 Taxonomy

There is plenty of available fuzzing tools often designed for specific situations and, in order to ease the choice of a particular tool, they can be put into different categories. This Section presents several common ways to categorize fuzzing tools.

**The attacker model :** Many available fuzzing tools are designed for a specific attacker model, could be white-box, black-box or grey-box, conditioning the amount of information the attacker has access to.

In the black-box model, the fuzzer is only aware of the current input to the P.U.T and the current output and no more. To take a decision, the bug oracle has only access to the target answer, same for the input space optimisation algorithms.

The white-box attacker model is the opposite one. The fuzzer has access to information about the P.U.T internals and design to elaborate a better space search strategy. It could for example make use of static analysis techniques and dynamic symbolic execution to identify critical and highly promising regions before P.U.T execution. In this model the P.U.T is instrumented, for example with a customized compilation process adding extra instructions and the fuzzer is able to gather a lot of informations about the target execution, especially with the help of the operating system and process monitoring tools.

The grey-box attacker model falls in-between the two previously discussed ones. The fuzzer does not have access to P.U.T internals, however the code could be instrumented and some sparse side-effects could be measured and used as metrics to be optimized thanks to the operating system and process monitoring.

The input space description : There is two main concurrent ways to describe the fuzz input space to the fuzzer. First approach is the model-based one where the space is defined by a formal model, often in the form of a language grammar. All the test-cases are generated according to this model. The other way is the mutation-based approach where the space is rather described by a single example. The fuzzer is then in charge of deriving this example sample by applying mutations to it, for example bitwise operations, permutations etc...

**The state awareness :** Many fuzzer implementations do not take in consideration the current state of the P.U.T internal state-machine. A state-aware fuzzer would rather try to exploit sequences of test-cases to bring the targeted state-machine in a particular state. This enables exploring in depth P.U.T statemachine to reach bugs which are not in the shallow states. It improves as well the reproducibility of the found bugs because it keeps trace of the sequence of successive states which led to it.

## Chapter 4

## Top-level engineering choices and strategy

### 4.1 Fuzzing at the T=1 abstraction level

The ISO7816-3 protocol stack illustrated in Figure 2.7 is a practical top-level view for discussing the strategic decisions which led to the fuzzer conception work. This schematic puts in evidence the three different abstraction layers in use by the protocol: the physical layer, the link layer and the application layer. The driver software aimed to be tested in this project is in charge of running the link layer, it receives application data from applets running on the card in the form of an APDU data structure, then it slices it up and passes the correct sequences of bytes to be sent to the physical layer. For this reason, in order to make sure to target specifically the driver implementation and not the application running on top of it, the decision is taken to fuzz at the link layer abstraction layer. This means that the test-cases forged and handled by the fuzzer are T=0 or T=1 data structures and are not APDU data structures. First, it brings the problem discussed in Section 4.2 because the smartcard readers available on the market are providing only the ability to handle APDUs with no control over the underlying layers. Secondly, because there is two distinct link layer protocols (T=0 and T=1, see Sections 2.6 and 2.7) the developed fuzzing tool has to be specific to each of those protocols. Previously realized projects, especially the implementation of the reader version of the T=1 protocol showed several interesting lacks in the protocol specification discussed in section 4.3. This led to prioritize first the development of the T=1 version.

### 4.2 Interfacing the targeted card with the fuzzer

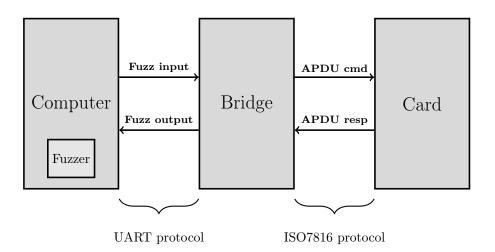

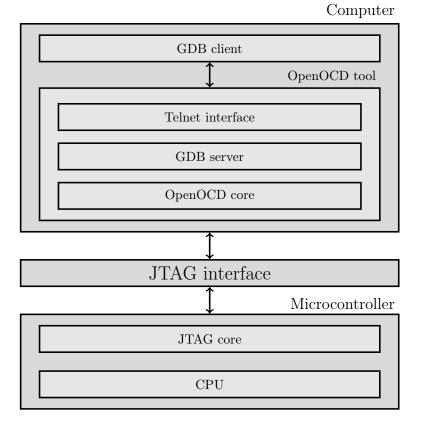

A fuzzing software is very demanding in computing resources, it needs to perform a lot of computations and data manipulations to derive the models, find optimal test-cases, check the answers and log the results. This is why it has to be run on a regular computer rather than on an embedded target. Moreover, the very large majority of existing tools are designed to run on a computer. The problem comes with the observation that computers do not natively have Internship Feedback

Fuzzing IS07816-3

Figure 4.1: Schematic illustration of the overall fuzzing setup. The fuzzer on the left side running on a computer is interfaced with the smartcard by the bridge device depicted in the middle.

an ISO7816 interface to deal with a smartcard, an intermediate interface like depicted in Figure 4.1 has to be added between the computer and the card. It could have been a regular USB reader from the market however those are not satisfying because they expose solely an interface at the APDU abstraction level and this is incompatible with the needs expressed in Section 4.1. There is a need for a reader capable of letting full control over T=0 and T=1 protocol flow. This could help to enforce some particular cases in the T=1 protocol and to push its state-machine into some previously identified and interesting states discussed in the next Section 4.3. As a consequence, it was decided to conceive a custom reader interface explained in Chapter 5 to match this need. As suggested in Figure 4.1, its functional role is to receive test-cases from the fuzzer running on the computer and then to retransmit them back to the card following the ISO7816 specification.

### 4.3 Identifying interesting areas to be fuzzed

Work previously done during the two first years of apprenticeship has led to a very precise knowledge and understanding of the T=1 protocol specification. This experience is useful to identify parts of the specified state-machine which are prone to software development errors and also to identify un-precise areas of the specifications which can lead to different interpretations depending on the developer. Several of these points are discussed in this section and are used to prioritize the test-cases with the most promising results.

The primarily targeted dysfunction in the card driver is the buffer overflow situation which generates big security concerns. It is a famous and frequently exploited bug where the attacker tries to mislead the program to write more data than it is expecting at a given place in memory. This enables the opponent to (re)write program memory in locations where it is not supposed to have access. The attacker can then change return values of functions or change informations

16th June 2020

Page 27/59

#### Internship Feedback

influencing the program execution flow. Typically this is achieved by inputting more bytes than it is currently expected, when the program writes these bytes into its own memory locations, it exceeds the initially allocated space and the bytes are being written in memory locations which were not initially allocated for it.

Applied to the smartcard and T=1 situation, given a naively implemented driver without any countermeasure, this kind of attacks could be, for example, performed by sending an information block (I-Block, see Section 2.7) with more data bytes than indicated in the LEN field. The driver would prepare a space in memory of the size of LEN bytes and store the LEN first received bytes at the expected location, then the received data bytes having indexes LEN+1, LEN+2 etc ... would be written outside the initially planned location, thus overwriting other, potentially critical, memory locations.

For these reasons it is planned to focus fuzzing efforts on the control of data field sizes. The T=1 I-Block LEN field are one way to influence this parameter, but it is also possible to mention the IFS S-Blocks used to negotiate maximum data field size (see Section 2.7).

Another point of interest is about the S-Blocks behaviour. These special blocks can be sent either by the reader or the card and are used to negotiate communication parameters or to resynchronize or abort a transaction (see Section 2.7). The resynchronization request is particularly interesting because previous development work on the T=1 protocol has put in evidence that its effect on the protocol state-machine is not perfectly well defined and specified. It is not very clear which settings have to be reset which should not be. The state where the state-machine has to come back after such a block is free to interpretation by the developer. This might lead to potential exploitable bugs for this project.

## Chapter 5

## The bridge connector between the fuzzer and the smartcard

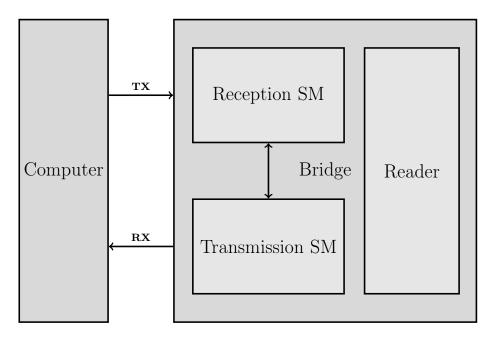

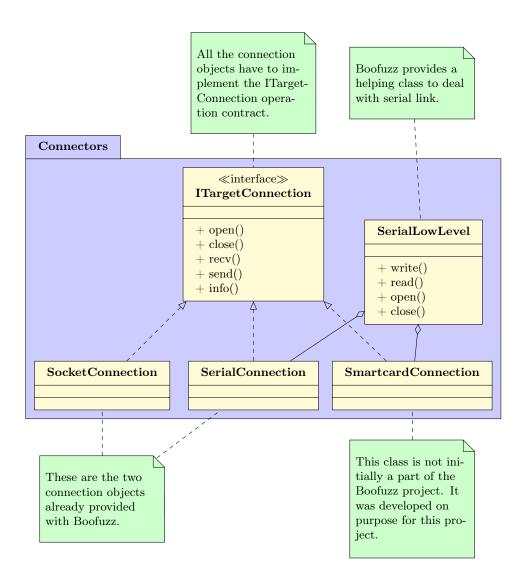

For the technical and strategic reasons given in Section 4 there is a need for an interface device connecting the card to the fuzzer running on a computer. In the context of this project, this device is called "bridge" and is conceptually placed in between the computer and the card as depicted in Figure 4.1. It has on its left an interface capable of dealing with a computer (discussed in Section 5.2) and on its right another interface able to communicate with the smartcard (discussed in Section 5.1). The purpose of this section is to go through the characteristics of the bridge device, explain the design choices and the implementation details.

### 5.1 The smartcard communication interface

The smartcard communication interface is a conceptual component of the bridge device in charge of enabling information exchange with the card. It is currently a full stack implementation of the ISO7816-3[12] reader protocol (including APDUs, T=0, T=1 and physical layer, respectively detailed in Sections 2.5, 2.6, 2.7, 2.8). On Figure 4.1, it is located in the entity labelled "Bridge" and deals with the right side of the schematic. It is also represented on Figure 5.7, labelled as "Reader". The implementation of this piece of software was part of this project and was preliminary coded and tested during the two first years of apprenticeship. Those kind of devices and implementations were already existing on the market at the time, however, for the reasons exposed in Section 4.2 it was chosen to re-implement it all from scratch. Especially it enables, for example, to deal directly with the link layer protocols when fuzzing (where the readers from the market are only exposing an APDU interface). Functionally, it is a piece of software which takes as an input a sequence of characters to be sent to the card, sends them, gets back the answer for the cards and finally serves back to answer as an output.

Using this custom reader implementation gives the possibility to have more sophisticated interactions with the card and also to enforce some specific behaviours at the low layers of the protocol stack which there is no control on from the applicative layer. This makes the fuzzing process more complete. For example, it is possible to directly interact with the character level (explained in

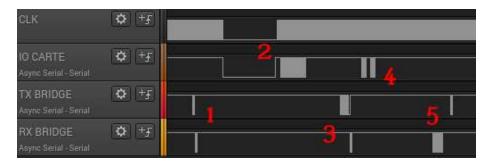

```

rv = READER_HAL_SendChar(pSettings, READER_HAL_PROTOCOL_T1, byte, TIMEOUT);

if(rv != READER_OK) return BRIDGE2_ERR;

rv = READER_HAL_RcvChar(pSettings, READER_HAL_PROTOCOL_T1, &byte, TIMEOUT);

if((rv != READER_OK) && (rv != READER_TIMEOUT)) return BRIDGE2_ERR;

```

Figure 5.1: Usage of the custom reader library *API* to deal with the physical layer, transmitting and receiving characters.

Section 2.8) by using the *API* pictured in Figure 5.1.

### 5.2 The computer communication interface

The computer communication interface is a bridge component enabling communication between the fuzzer running on the computer and the bridge. Functionally it is a piece of software inside the bridge which takes as an input informations from the fuzzer, typically a test case to be applied to the card or configuration informations, then forwards them to the bridge state machine. It is also in charge of sending back to the fuzzer all the necessary feedbacks.

The choice of the communication technology across computer and bridge was tough because various technologies can perform the same task. Mainly the possibilities across USB, Ethernet, TCP/IP and serial were discussed. The USB technology provides great throughput and reliability however such high performances are not needed in this case and the software development overhead and the cost in CPU time would have been too important. Moreover, the chosen fuzzing tool discussed in Section 6.1 does not provide natively a USBinterface. For those reasons USB was rapidly put apart. Ethernet could have been an interesting choice but it is also slightly too complex for our purpose.. The microcontroller being used in this project (see Section 5.3) has a native hardware support for Ethernet however, the fuzzer chosen in Section 6.1 supports natively only TCP/IP connections. So it would be necessary to implement the TCP/IP protocol stack in software, which is an important overhead in performances, development time and an important source of errors and bugs. Thus, TCP/IP and Ethernet were put apart too. The serial connection was found to be very promising by being very lightweight with full hardware support for the microcontroller side and a native implementation in the selected fuzzing tool (see Section 6.1).

### 5.3 The hardware running the bridge software

As specified in Sections 5.1 and 5.2, the bridge is an hardware device physically doing the link between the computer and the card and is expected to be able to run the software implementation of the ISO7816-3 protocol from one side and provide a serial interface from the other side. It is also expected to have the computing capacity to run some middleware logic in the form of a state machine in order to make the translation across protocols and eventually to execute actions depending on the situation. These expectations are quite low so

#### Internship Feedback

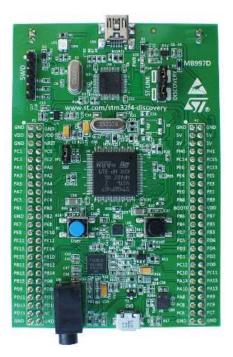

Figure 5.2: Picture of the STM32F407 Discovery board provided by STMicroelectronics taken from its user manual[17]. The main chip in the middle is the STM32F407 microcontroller, which is surrounded by all the necessary equipment to make it run while easing programming and debugging.

a basic single core microcontroller with UART hardware peripherals is sufficient. As long as the reader library mentioned in Section 5.1 has been developed for an STM32F407 microcontroller target, the decision was taken to keep the same target to host the whole bridge device. Given the fact that this device is not aimed to be industrialized, sold or distributed, the pricing difference across the different models and references are not criteria of choice. For the same reasons it was also decided to design the whole project on the associated prototyping board widely provided by the STMicroelectronics company called the "discovery board" under the STM32F407G-DISC1 reference.

This prototyping board, visible on Figure 5.2, comes with a very complete STM32F407[16] microcontroller and all the surrounding equipment necessary to execute programs and to ease the development. For example it provides a regulated power source, a crystal oscillator, *USB* to *UART* conversion chips to ease interfacing with other devices, great connectors to ease pluging and programming and debugging hardware.

The STM32F407 is a 32 bits architecture microcontroller chip manufactured by the STMicroelectronics company. It integrates a powerful ARM Cortex-M4 core and very numerous peripherals all interconnected with an AHB internal bus. Especially, it comes with very configurable UART peripherals that are going to be discussed later in this report. Also, this internal AHB bus is synchronized at 128MHz in this project setup, it enables to achieve a great processing speed compared to the protocols involved in computer and card communication

interfaces. Indeed, the magnitude order for the transmission of a character on both sides is one millisecond. This gives the comfort of coding the middleware logic without caring too much about the real time constraints.

Another important criteria of choice for this device were the characteristics of its integrated UART peripherals. The aim of this logic circuitry is to handle a whole UART character transmission without involving the CPU in order to save CPU time. As explained in Section 2.8, the physical layer of the ISO7816-3 protocol is similar to UART process to transmit and receive characters. The UART peripherals embedded in this microcontroller are sophisticated enough and flexible enough to get a behaviour matching the ISO7816-3 standard. Especially, it supports half-duplex communication, precise tuning of the number of stop-bits, introduction of guard-time in-between characters and error detection. A fractional baudrate generator enables easy and precise clock source generation at destination of the card and the configuration registers enable to produce frames with the right structure (start bit, 8 bits payload and parity bit). This way, it saves time on the development of the physical layer and unloads the CPU to save performances for dealing with the higher layers.

### 5.4 The first, naive, strategy

Two different approaches have been used to conceive bridges state machine. This Section describes the approach which was used as a first shot, it advantages and the drawbacks that led to the second approach detailed in Section 5.5.

The first approach was focused on keeping it simple and getting some exploitable results as fast as possible. It consisted in a simple byte repeater between the two interfaces previously described in Sections 5.1 and 5.2. When the bridge was receiving a character from the computer on the serial interface, it repeated it immediately back on the ISO7816 interface and vice versa.

This has several advantages, first the implementation of the state machine is extremely simple, thus avoiding bugs and saving development time. The second point is that, as long as the chosen fuzzer natively supports serial interface (see Section 6.1) there is no need to work on a plugin interface in the fuzzer side, it is completely transparent.

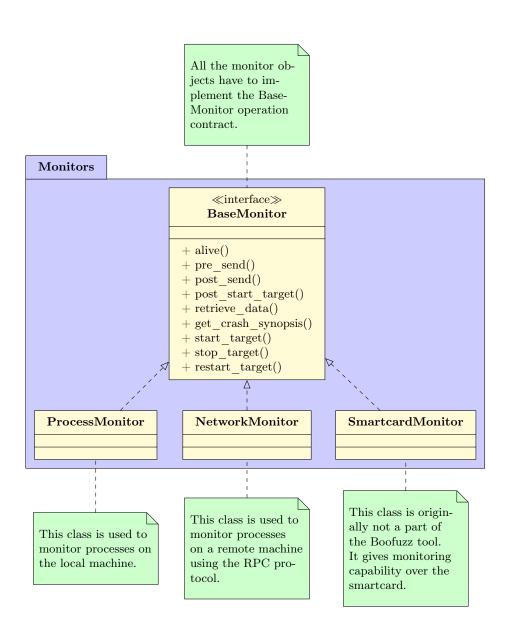

This method was working well in a matter of few days, however it suffered from several serious lacks. Some very specific cases were problematic, for example if the card starts to answer before the fuzzer finished to send its test case to the card, there will be an access conflict over the ISO7816 half-duplex transmission line. This could easily happen in a fuzzing situation were the length field (see Section 2.7) is typically going to be altered to a smaller value to trigger a buffer overflow. Moreover, it would be very practical if the fuzzer could request the reader to perform some control actions like resetting the card or changing communication parameters and this is not possible with this design. The reset operation is particularly important because the fuzzer chosen in Section 6.1 is state-aware and studying which sequence of actions is leading to a bug, so it is important to be able to replace the card state machine in a very well known state after each test case. Being able to change physical layer communication parameters also offers great further work perspectives by hardening the fuzzing process by playing with the physical layer. These observations led to the method presented in Section 5.5.

Figure 5.3: Illustration of the block structure of the communication protocol implemented between the computer and the bridge.

### 5.5 Second approach, the implemented protocol

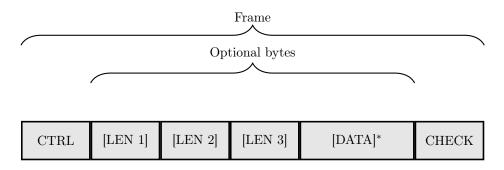

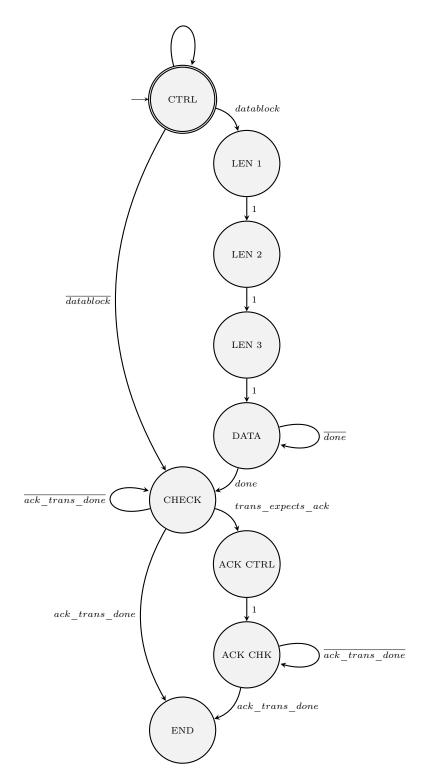

The solution considered to solve the issues mentioned in Section 5.4 is to implement a real application layer communication protocol over the serial link to handle properly the data interchange and control flow information. The data to send and actions to execute are encapsulated in block structures as depicted in Figure 5.3. These block structures can be represented as frames composed of the following bytes sequences :

First comes the mandatory CTRL byte, it is used to encode the type of the block being currently sent. It can be one of the following values :

- DATA\_BLOCK, its purpose is to carry a data payload. Typically it carries the data to be sent by the reader or the response from the card.

- ACK BLOCK is used to acknowledge a previously received block.

- NACK\_BLOCK is used to indicate an error at block reception.

- COLD\_RST\_BLOCK is a control block used to ask the reader device to perform a cold reset operation on the card.

Then, in case of a data block, the three next bytes, LEN1, LEN2 and LEN3 are big-endian encoding the length (in number of bytes) of the subsequent data field. They are then followed right after by the optional data bytes. Finally, the frame ends with a mandatory CHECK byte carrying an LRC error detection code.

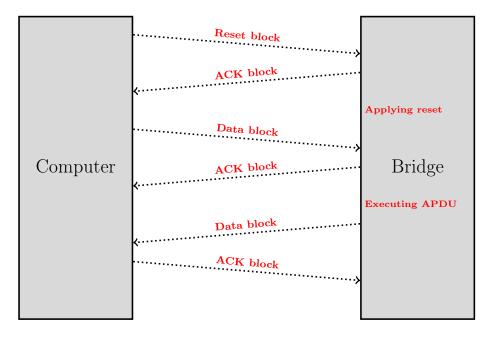

The protocol operation is then quite simple, each block sent by a device has to be acknowledged by the other device with the dedicated block. The acknowledgement block does not need to be acknowledged. Figure 5.4 describes how the fuzzer and the bridge are interacting over time in order to process a fuzz iteration.

First, the computer sends to the bridge a cold reset block to tell the reader to execute the cold reset procedure on the card. After the reception of this information, the bridge processes it and acknowledges the correct reception of this block by sending back to the computer an ACK block. After ACK reception, the computer transmits a data block containing fuzzers payload to be sent by the reader. If it is correctly received, the bridge sends back an ACKblock. The bridge now internally retrieves the data from the block and pass

#### Internship Feedback

Fuzzing IS07816-3

Figure 5.4: Illustration of the block structure of the communication protocol implemented between the computer and the bridge.